### University of Strathclyde Department of Electronic and Electrical Engineering

# DC-DC Converter Designs for Medium and High Voltage Direct Current Systems

by

Islam Azmy Gowaid

A thesis presented in fulfilment of the requirements for the degree of Doctor of Philosophy

March 2017

This thesis is the result of the author's original research. It has been composed by the author and has not been previously submitted for examination which has led to the award of any degree.

The copyright of this thesis belongs to the author under the terms of the United Kingdom Copyright Acts as qualified by University of Strathclyde Regulation 3.50. Due acknowledgement must always be made of the use of any material contained in, or derived from, this thesis.

Signed: I. A. Gowaid

Date: 25.03.2017

### Acknowledgements

I would like to express my deep appreciation to my supervisors Prof. Barry Williams, Dr Derrick Holliday, and Dr Grain Adam for their support, guidance, and advice throughout this research.

I also would like to thank Dr Ahmed Massoud, Dr Shehab Ahmed, Dr Ayman Abdel-Khalik, and Dr Ahmed Elserougi for their valuable technical contributions, contribution to the funding of this research, and for their important role in my research career.

Thanks to colleagues and staff at PEDEC, I have had lots of unforgettable moments not only at the university but also around Scotland. On a personal level, Dr Grain Adam, Fred Page, Joe Burr, Yanni Zhong, Ahmed Darwish, Dimitrios Vozikis, Kamyab Givaki, Habib Rahman, Jin Sha, and Luiz Villa have all left a remarkable impact on me. I extend my thanks to them and the rest of the team for assistance, useful discussions, and the encouraging atmosphere.

Finally, a great deal of thanks goes to my family specifically my loving mother and my wonderful wife for their unlimited care, support, and encouragement.

# Acronyms

| AAC    | Alternate Arm Converter                      |

|--------|----------------------------------------------|

| AC     | Alternate Current                            |

| ATAC   | Asymmetric Transition Arm Converter          |

| AP-TAC | Asymmetric Parallel Transition Arm Converter |

| C2L    | Cascaded Two-Level Converter                 |

| CS     | Complementary Switching                      |

| DAB    | Dual Active Bridge                           |

| DC     | Direct Current                               |

| DCCB   | Direct Current Circuit Breaker               |

| FB     | Full Bridge                                  |

| GSC    | Grid Side Converter                          |

| HB     | Half Bridge                                  |

| HVDC   | High Voltage Direct Current                  |

| IGBT   | Insulated Gate Bipolar Transistor            |

| IGCT   | Integrated gate commutated thyristor         |

| LCC    | Line Commutated Converter                    |

| MMC    | Modular Multilevel Converter                 |

| MTDC   | Multi-terminal Direct Current                |

| MTAC   | Modular Transition Arm Converter             |

| MP-TAC | Modular Parallel Transition Arm Converter    |

| NCS    | Non-Complementary Switching                  |

| NDC    | Nested DC Converter                          |

| NLC    | Nearest Level Control                        |

| NPC    | Neutral Point Clamped                        |

| PCC    | Point of Common Coupling                     |

| P-TAC  | Parallel Transition Arm Converter            |

| PV     | Photovoltaic                                 |

| PWM    | Pulse Width Modulation                       |

| Q2LC   | Quasi Two-Level Converter                    |

| SHE    | Selective Harmonic Elimination               |

| SP-TAC | Symmetric Modular Transition Arm Converter   |

| SVM    | Space Vector Modulation                      |

| THD    | Total Harmonic Distortion                    |

| VSC    | Voltage Source Converter                     |

# List of Symbols

| A                  | AC transformer turns ratio                                                               |

|--------------------|------------------------------------------------------------------------------------------|

| $C_{cell}, C_{sm}$ | Cell (submodule) capacitance                                                             |

| $C_{dc}$           | DC-link capacitance                                                                      |

| $C_{gp}$           | Cell subgroup capacitance of the primary side                                            |

| $C_{gs}$           | Cell subgroup capacitance of the secondary side                                          |

| $E_{ m MMC}$       | MMC stored energy                                                                        |

| $E_s$              | Specific MMC stored energy (kJ/MVA)                                                      |

| $E_{ac}$           | AAC arm energy exchange with the ac circuit                                              |

| $E_{dc}$           | AAC arm energy exchange with the dc circuit                                              |

| $F_d$              | d-axis feedforward term                                                                  |

| $F_q$              | q-axis feedforward term                                                                  |

| arphi              | Phase shift angle or load angle                                                          |

| $i_{dc}$           | DC current                                                                               |

| ісм                | Common mode arm current                                                                  |

| $i_d$              | d-axis current component                                                                 |

| $I_q$              | q-axis current component                                                                 |

| $I_H$              | The high voltage side dc current                                                         |

| $I_L$              | The low voltage side dc current                                                          |

| k                  | Harmonic order                                                                           |

| L                  | Inductance                                                                               |

| $L_s$              | Coupling transformer leakage inductance                                                  |

| L <sub>tr</sub>    | GSC ac transformer leakage inductance                                                    |

| m                  | Modulation index                                                                         |

| $m_k$              | Modulation index of harmonic order $k$                                                   |

| Ν                  | Number of cells per arm                                                                  |

| $N_s$              | Number of cell subgroups per arm                                                         |

| n                  | Number of cells per cell subgroup                                                        |

| р                  | The derivative operator                                                                  |

| $P_{dc}$           | DC power flow                                                                            |

| $P_g$              | Active power exchanged with the ac grid                                                  |

| $Q_g$              | Reactive power exchanged with the ac grid                                                |

| ρ                  | DC ratio (Ratio between the primary and secondary dc voltages both referred to one side) |

| R                  | MMC arm Resistance                                                                       |

| R <sub>tr</sub>  | GSC ac transformer resistance                                                    |

|------------------|----------------------------------------------------------------------------------|

| $S_{MMC}$        | MMC apparent power rating                                                        |

| $T_d$            | Dwell time                                                                       |

| $T_{sc}$         | Total switching time of one cell                                                 |

| $T_t$            | Transition time between the two dominant voltages of the trapezoidal ac waveform |

| Vd               | d-axis voltage component                                                         |

| $v_q$            | q-axis voltage component                                                         |

| $V_{dcp}$        | Primary side dc voltage                                                          |

| $V_{dc}$         | DC voltage                                                                       |

| V <sub>dcs</sub> | Secondary side dc voltage                                                        |

| $V_H, V_{dcH}$   | The high voltage side dc voltage                                                 |

| $V_L, V_{dcL}$   | The low voltage side dc voltage                                                  |

| $\omega_s$       | Switching angular frequency                                                      |

| $\omega_e$       | grid angular frequency                                                           |

# Subscripts

| 8   | AC grid value        |

|-----|----------------------|

| g   | AC grid value        |

| р   | Primary side value   |

| max | maximum value        |

| min | minimum value        |

| S   | Secondary side value |

### Abstract

DC fault protection is one challenge impeding the development of multi-terminal dc grids. The absence of manufacturing and operational standards has led to many point-to-point HVDC links built at different voltage levels, which creates another challenge. Therefore, the issues of voltage matching and dc fault isolation in high voltage dc systems are undergoing extensive research and are the focus of this thesis. The modular multilevel design of dual active bridge (DAB) converters is analysed in light of state-of-the-art research in the field. The multilevel DAB structure is meant to serve medium and high voltage applications. The modular design facilitates scalability in terms of manufacturing and installation, and permits the generation of an output voltage with controllable dv/dt. The modular design is realized by connecting an auxiliary soft voltage clamping circuit across each semiconductor switch (for instance insulated gate bipolar transistor – IGBT) of the series switch arrays in the conventional two-level DAB design. With auxiliary active circuits, series connected IGBTs effectively become series connection of half-bridge submodules (cells) in each arm, resembling the modular multilevel converter (MMC) structure. For each half-bridge cell, capacitance for quasi-square wave (quasi twolevel) operation is significantly smaller than typical capacitance used in MMCs. Also, no bulky arm inductors are needed. Consequently, the footprint, volume, weight and cost of cells are lower. Four switching sequences are proposed and analysed in terms of switching losses and operation aspects. A design method to size converter components is proposed and validated. Soft-switching characteristics of the analysed DAB are found comparable to the case of a two-level DAB at the same ratings and conditions.

A family of designs derived from the proposed DAB design are studied in depth. Depending on the individual structure, they may offer further advantages in term of installed semiconductor power, energy storage, conduction losses, or footprint. A non-isolated dc-dc converter topology which offers more compact and efficient station design with respect to isolated DAB – yet without galvanic isolation – is studied for quasi two-level (trapezoidal) operation and compared to the isolated versions.

In all the proposed isolated designs, active control of the dc-dc converter facilitates dc voltage regulation and near instant isolation of pole-to-pole and pole-to-ground dc faults within its protection zone. The same can be achieved for the considered non-isolated dc-dc converter topology with additional installed semiconductors.

Simulation and experimental results are presented to substantiate the proposed concepts.

# Contents

| Ackr    | nowle | dgements                                             | 2  |

|---------|-------|------------------------------------------------------|----|

| Acro    | nyms  | s                                                    |    |

| List o  | of Sy | mbols                                                | 4  |

| Abstrac | ct    |                                                      | 6  |

| Chapter | r 1   | Introduction                                         |    |

| 1.1     | Bac   | ckground                                             |    |

| 1.2     | Mu    | lti-terminal dc networks                             | 16 |

| 1.3     | Mo    | tivation and objectives                              |    |

| Chapter | r 2   | DC-DC Converters for DC Networks                     |    |

| 2.1     | Ha    | rd switched DC-DC converters                         |    |

| 2.2     | DC    | /AC bridge designs                                   |    |

| 2.2     | 2.1   | The two-level voltage source converters              |    |

| 2.2     | 2.2   | Multilevel voltage source converters                 |    |

| 2.2     | 2.3   | The modular multilevel converter (MMC)               |    |

| 2.2     | 2.4   | The Alternate arm converter                          |    |

| 2.3     | Iso   | lated dc-dc converter designs                        |    |

| 2.3     | 3.1   | Two-level dual active bridge (2L-DAB)                |    |

| 2.3     | 3.2   | Multi-module DAB                                     |    |

| 2.3     | 3.3   | Resonant DAB designs                                 |    |

| 2.3     | 3.4   | MMC-based and AAC-based DAB designs                  |    |

| 2.4     | No    | n-isolated dc-dc converter designs                   |    |

| 2.4     | 4.1   | Non-isolated DAB designs                             |    |

| 2.4     | 4.2   | Transformerless dc-dc converter designs              | 61 |

| 2.5     | Des   | sirable Features in Candidate HVDC-DC Converter      |    |

| Chapter | r 3   | DAB Structure Based on the Quasi Two-Level Converter |    |

| 3.1     | Tra   | pezoidal operation of the DAB dc-dc converter        |    |

| 3.2     | The   | e Quasi Two-level Converter                          |    |

| 3.2     | 2.1   | Synthesis of the trapezoidal voltage waveform        |    |

| 3.2     | 2.2   | Grouping of half bridge cells in a Q2LC              |    |

|      | 3.2. | 3   | Analysis of the trapezoidal ac voltage                        | 82  |

|------|------|-----|---------------------------------------------------------------|-----|

|      | 3.2. | 4   | Q2LC switching sequences                                      | 87  |

|      | 3.2. | 5   | Dwell time limits                                             | 93  |

|      | 3.2. | 6   | Operation of the Q2LC under CS and NCS switching sequences    | 93  |

| 3.3  | 3    | Q2I | C-based DAB component sizing                                  | 97  |

|      | 3.3. | 1   | Q2LC-based DAB ac link voltages and currents                  | 98  |

|      | 3.3. | 2   | Semiconductor devices current rating                          | 102 |

|      | 3.3. | 3   | Cell capacitance sizing                                       | 104 |

| 3.4  | 1    | Q2I | C-based DAB arm energy fluctuations                           | 106 |

| 3.5  | 5    | Q2I | C-based DAB numerical simulation                              | 109 |

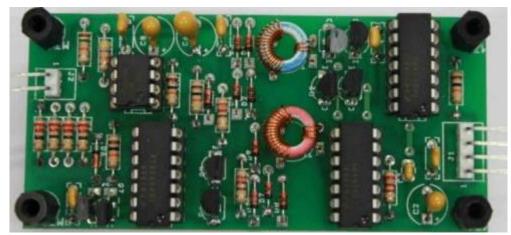

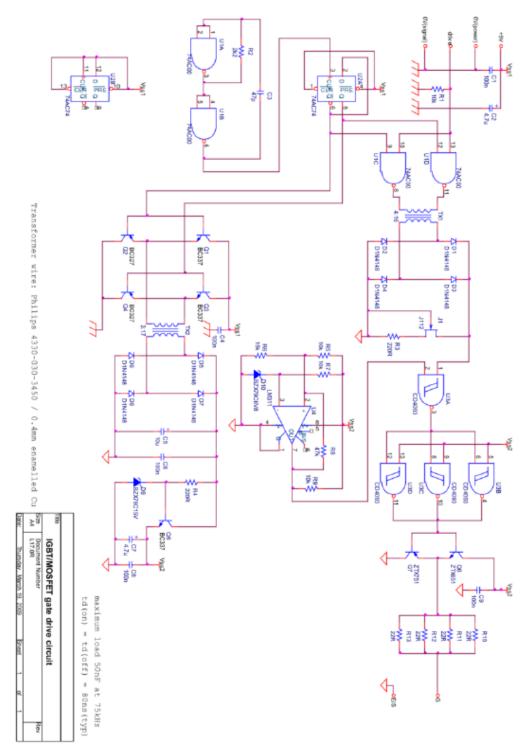

| 3.6  | 5    | Exp | perimental validation of the Q2LC concept                     | 112 |

| 3.7  | 7    | Sun | nmary                                                         | 115 |

| Chap | oter | 4   | DAB Structure Based on Transition Arm Converter Designs       | 119 |

| 4.1  | 1    | CTI | B-based F2F dc-dc converter                                   | 119 |

|      | 4.1. | 1   | Switching devices ratings                                     | 121 |

|      | 4.1. | 2   | Chainlink cells capacitance design                            | 121 |

|      | 4.1. | 3   | Chainlink energy fluctuations                                 | 122 |

| 4.2  | 2    | CTI | B-based F2F converter numerical simulation                    | 124 |

| 4.3  | 3    | The | parallel transition arm converter (P-TAC)                     | 126 |

|      | 4.3. | 1   | The asymmetric PTAC (AP-TAC)                                  | 127 |

|      | 4.3. | 2   | The symmetric PTAC (SP-TAC)                                   | 132 |

|      | 4.3. | 3   | The modular PTAC (MP-TAC)                                     | 136 |

|      | 4.3. | 4   | MP-TAC based F2F converter numerical simulation               | 139 |

| 4.4  | 1    | The | transition arm converter (TAC)                                | 140 |

|      | 4.4. | 1   | The asymmetric transition arm converter (ATAC)                | 140 |

|      | 4.4. | 2   | ATAC-based F2F converter numerical simulation                 | 143 |

|      | 4.4. | 3   | The symmetric TAC (STAC) and the modular TAC (MTAC)           | 144 |

|      | 4.4. | 4   | MTAC-based F2F dc-dc converter numerical simulation           | 147 |

| 4.5  | 5    | Exp | perimental validation                                         | 148 |

| 4.6  | 5    | Sun | nmary                                                         | 152 |

| Chap | oter | 5   | Characteristics of Birdge Structures for F2F DC-DC Converters | 157 |

| 5.1  | 1    | DC  | -link filter capacitor design                                 | 157 |

| 5.2                                                                                                                                         | Mo                                                                                             | dulation index control                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| 5.                                                                                                                                          | 2.1                                                                                            | Inter-switching modulation                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                              |

| 5.                                                                                                                                          | 2.2                                                                                            | Clamp modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                              |

| 5.                                                                                                                                          | 2.3                                                                                            | Phase shift modulation                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                              |

| 5.3                                                                                                                                         | Sof                                                                                            | t switching characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                              |

| 5.4                                                                                                                                         | Ser                                                                                            | niconductor effort and energy storage capacity                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                              |

| 5.5                                                                                                                                         | Co                                                                                             | nduction losses                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                              |

| 5.6                                                                                                                                         | DC                                                                                             | fault blocking capability of F2F dc-dc converters                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                              |

| 5.                                                                                                                                          | 6.1                                                                                            | Steady-state controllers                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                              |

| 5.                                                                                                                                          | 6.2                                                                                            | Operation under a dc fault                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                              |

| 5.                                                                                                                                          | 6.3                                                                                            | Three terminal HVdc test system                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                              |

| 5.7                                                                                                                                         | Fau                                                                                            | lt-tolerant voltage matching of multiple HVDC lines                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                              |

| 5.                                                                                                                                          | 7.1                                                                                            | Star versus ring dc nodes                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                              |

| 5.                                                                                                                                          | 7.2                                                                                            | Improved Efficiency with Solid State DCCBs                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                              |

| 5.                                                                                                                                          | 7.3                                                                                            | Lower DCCB stress under fault                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                              |

| 5                                                                                                                                           | 7.4                                                                                            | Voltage matching dc node topologies                                                                                                                                                                                                                                                                                                                                                                                                                                | 203                                                                                                          |

| 5.                                                                                                                                          | /.4                                                                                            | vorage matering de node topologies                                                                                                                                                                                                                                                                                                                                                                                                                                 | 203                                                                                                          |

| 5.8                                                                                                                                         |                                                                                                | nmary                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                              |

|                                                                                                                                             | Sur                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                              |

| 5.8                                                                                                                                         | Sur<br>er 6                                                                                    | nmary                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                              |

| 5.8<br>Chapte                                                                                                                               | Sur<br><u>r 6</u><br>The                                                                       | nmary<br>A Non-Isolated Nested DC-DC Converter with Trapezoids                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                              |

| 5.8<br>Chapte<br>6.1                                                                                                                        | Sur<br>er 6<br>The<br>Nu                                                                       | nmary<br>A Non-Isolated Nested DC-DC Converter with Trapezoids<br>e Nested DC-DC Converter                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                              |

| 5.8<br>Chapte<br>6.1<br>6.2<br>6.3                                                                                                          | Sur<br>r 6<br>The<br>Nur<br>Asy                                                                | nmary<br>A Non-Isolated Nested DC-DC Converter with Trapezoids<br>e Nested DC-DC Converter<br>merical simulation of MTAC-based asymmetric NDC                                                                                                                                                                                                                                                                                                                      |                                                                                                              |

| 5.8<br>Chapte<br>6.1<br>6.2<br>6.3<br>6.3                                                                                                   | Sur<br>r 6<br>The<br>Nur<br>Asy                                                                | nmary<br>A Non-Isolated Nested DC-DC Converter with Trapezoids<br>e Nested DC-DC Converter<br>merical simulation of MTAC-based asymmetric NDC<br>ymmetric Nested DC-DC converter DC fault handling                                                                                                                                                                                                                                                                 | 206<br>208<br>208<br>208<br>215<br>215<br>215<br>216                                                         |

| 5.8<br>Chapte<br>6.1<br>6.2<br>6.3<br>6.3                                                                                                   | Sur<br>r 6<br>The<br>Nur<br>Asy<br>3.1<br>3.2                                                  | nmary<br>A Non-Isolated Nested DC-DC Converter with Trapezoids<br>e Nested DC-DC Converter<br>merical simulation of MTAC-based asymmetric NDC<br>ymmetric Nested DC-DC converter DC fault handling<br>High voltage side DC fault                                                                                                                                                                                                                                   | 206<br>208<br>208<br>208<br>215<br>215<br>215<br>216<br>220                                                  |

| 5.8<br>Chapte<br>6.1<br>6.2<br>6.3<br>6.<br>6.<br>6.4                                                                                       | Sur<br>r 6<br>The<br>Nur<br>Asy<br>3.1<br>3.2                                                  | nmary<br>A Non-Isolated Nested DC-DC Converter with Trapezoids<br>e Nested DC-DC Converter<br>merical simulation of MTAC-based asymmetric NDC<br>ymmetric Nested DC-DC converter DC fault handling<br>High voltage side DC fault<br>Low voltage side DC fault                                                                                                                                                                                                      |                                                                                                              |

| 5.8<br>Chapte<br>6.1<br>6.2<br>6.3<br>6.<br>6.4<br>6.4                                                                                      | Sur<br>r 6<br>The<br>Nur<br>Asy<br>3.1<br>3.2<br>Syr                                           | nmary<br>A Non-Isolated Nested DC-DC Converter with Trapezoids<br>e Nested DC-DC Converter<br>merical simulation of MTAC-based asymmetric NDC<br>ymmetric Nested DC-DC converter DC fault handling<br>High voltage side DC fault<br>Low voltage side DC fault<br>nmetric Nested DC-DC converter DC fault handling                                                                                                                                                  | 206<br>208<br>208<br>215<br>215<br>215<br>216<br>220<br>221<br>221                                           |

| 5.8<br>Chapte<br>6.1<br>6.2<br>6.3<br>6.<br>6.4<br>6.4                                                                                      | Sur<br>r 6<br>The<br>Nur<br>Asy<br>3.1<br>3.2<br>Syr<br>4.1<br>4.2                             | A Non-Isolated Nested DC-DC Converter with Trapezoids<br>e Nested DC-DC Converter<br>merical simulation of MTAC-based asymmetric NDC<br>ymmetric Nested DC-DC converter DC fault handling<br>High voltage side DC fault<br>Low voltage side DC fault<br>nmetric Nested DC-DC converter DC fault handling<br>Pole-to-pole dc fault                                                                                                                                  | 206<br>208<br>208<br>215<br>215<br>215<br>216<br>220<br>221<br>221<br>221<br>222                             |

| 5.8<br>Chapte<br>6.1<br>6.2<br>6.3<br>6.<br>6.<br>6.4<br>6.<br>6.5                                                                          | Sur<br>r 6<br>The<br>Nur<br>Asy<br>3.1<br>3.2<br>Syr<br>4.1<br>4.2                             | A Non-Isolated Nested DC-DC Converter with Trapezoids<br>e Nested DC-DC Converter<br>merical simulation of MTAC-based asymmetric NDC<br>ymmetric Nested DC-DC converter DC fault handling<br>High voltage side DC fault<br>Low voltage side DC fault<br>nmetric Nested DC-DC converter DC fault handling<br>Pole-to-pole dc fault<br>Pole-to-ground dc fault with symmetric monopolar NDC                                                                          | 206<br>208<br>208<br>215<br>215<br>215<br>216<br>220<br>221<br>221<br>221<br>222<br>224                      |

| 5.8<br><b>Chapte</b><br>6.1<br>6.2<br>6.3<br>6.<br>6.<br>6.4<br>6.<br>6.<br>6.5<br>6.                                                       | Sur<br>r 6<br>The<br>Nur<br>Asy<br>3.1<br>3.2<br>Syr<br>4.1<br>4.2<br>Fro                      | A Non-Isolated Nested DC-DC Converter with Trapezoids<br>e Nested DC-DC Converter                                                                                                                                                                                                                                                                                                                                                                                  | 206<br>208<br>208<br>215<br>215<br>215<br>216<br>220<br>221<br>221<br>221<br>222<br>224<br>224               |

| 5.8<br><b>Chapte</b><br>6.1<br>6.2<br>6.3<br>6.<br>6.<br>6.4<br>6.<br>6.<br>6.5<br>6.                                                       | Sur<br>r 6<br>The<br>Nur<br>Asy<br>3.1<br>3.2<br>Syr<br>4.1<br>4.2<br>Fro<br>5.1<br>5.2        | A Non-Isolated Nested DC-DC Converter with Trapezoids<br>e Nested DC-DC Converter                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                              |

| 5.8<br><b>Chapte</b><br>6.1<br>6.2<br>6.3<br>6.<br>6.<br>6.4<br>6.<br>6.<br>6.5<br>6.<br>6.<br>6.<br>6.<br>6.<br>6.<br>6.<br>6.<br>6.<br>6. | Sur<br>r 6<br>The<br>Nur<br>Asy<br>3.1<br>3.2<br>Syr<br>4.1<br>4.2<br>Fro<br>5.1<br>5.2<br>Sur | A Non-Isolated Nested DC-DC Converter with Trapezoids<br>e Nested DC-DC Converter<br>merical simulation of MTAC-based asymmetric NDC<br>ymmetric Nested DC-DC converter DC fault handling<br>High voltage side DC fault<br>Low voltage side DC fault<br>nmetric Nested DC-DC converter DC fault handling<br>Pole-to-pole dc fault<br>Pole-to-pole dc fault<br>nt-to-Front converter versus the Nested DC-DC Converter<br>Semiconductor Effort<br>Conduction Losses | 206<br>208<br>208<br>215<br>215<br>215<br>216<br>220<br>221<br>221<br>222<br>224<br>224<br>224<br>229<br>231 |

| 7.2 Future Research                       |  |

|-------------------------------------------|--|

| References                                |  |

| APPENDEX A: Sample Codes for verification |  |

| APPENDIX B: Publications                  |  |

### Introduction

### 1.1 Background

The global concerns of escalating environmental problems and alarming climate change have put immense pressure on policy makers to enforce greenhouse gas emission capping targets on various economic sectors worldwide. In a bid to prevent dangerous anthropogenic interference with the climate system, the United Nations Framework Convention on Climate Change (UNFCCC) has been negotiated at the Earth Summit in Rio de Janeiro in 1992 [1]. The UNFCCC was extended in 1997 by the Kyoto Protocol which entered into force in 2005 with 192 parties involved [2]. In the 2015 United Nations Climate Change Conference, held in Paris, the 195 participating parties agreed by consensus to so called 'Paris Agreement'. Despite the absence of clear mechanisms or specific emission-reduction targets, the Paris Agreement binds member states to commit to keeping global warming well below 2° C once 55 states who produce combined at least 55% of global greenhouse gas have ratified the agreement. According to some scientists, a 1.5 °C goal for instance will require zero greenhouse gas emissions globally sometime between 2030 and 2050 [3].

These ambitious carbon reduction targets are a major driving force towards mixing up the global energy resource with a significant share of renewable and green energy sources. As of the end of 2015, a total of 1849 GW of renewable installed energy resources were integrated to electricity grids worldwide. Hydro power contributes the major section of the renewable mix by 1064 GW, followed by 433 GW of installed wind power, 227 GW global solar PV installations, 106 GW of biomass, and 13.2 GW of geothermal power generation [4].

The inherent stochasticity of many of the renewable energy supplies – primarily wind and solar power – brings about stability challenges to electricity grids. Phasing out significant portions of controlled conventional generation plants (e.g., coal-fired power plants or nuclear plants) may upset the intricate demand-supply balance mechanisms and lead to intolerable frequency swings. The steady spinning reserve traditionally provided by conventional plants to handle such power imbalances is harder to manage by stochastic renewable resources.

Despite these technical challenges, the political pressure mounting worldwide – as seen for instance in Germany – leaves less room in future energy scenarios for conventional generation in the energy supply mix for provision of base load and other ancillary services. In consequence, regional and international grid interconnections appear inevitable in such an energy supply scenario to retain system security by continuous power exchange between national grids. High capacity transmission lines are also needed to relieve congested power corridors in the current and future power trading scenarios with an ever-increasing power demand. In consequence, there is a pressing need for environmentally-friendly technology capable of transmitting bulk amounts of power over large distances with tolerable levels of losses and high degrees of security of supply.

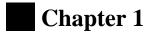

For decades, high voltage dc (HVDC) grids have been viewed as a key element in building anticipated high capacity transmission systems. At high power and long distances, traditional ac transmission systems become more expensive than equivalent dc lines. With overhead transmission, bipolar HVDC lines require smaller towers and significantly less right-of-way than equivalent three phase double circuit ac lines. The cost break-even point is at about 600-800km distance (see Figure 1.1). For underground or subsea transmission, high ac cable charging currents render system design and efficiency infeasible such that dc is favoured beyond about 50 km [5], [6], [7], [8]. Nevertheless, realization of dc transmission systems at high voltage and high power has always been surrounded by challenges ranging from the need for suitable business models to major technical obstacles and, with certain technologies, lack of operational experience.

Despite the challenges highlighted above the concept continues to gain momentum across the industry. In particular two major projects are set to benefit from HVDC technology; namely the 'European Supergrid' [9] and 'Desertec' [10]. In its early phases, the European Supergrid aims at interconnecting at least the power grids of several European countries along with offshore wind farms dispersed around the North Sea and major hydropower plants (see Figure 1.2).

Figure 1.1 Cost comparison between ac and dc transmission lines with respect to line length.

Figure 1.2 The European Supergrid project to deliver the North Sea offshore wind energy to European onshore grids.

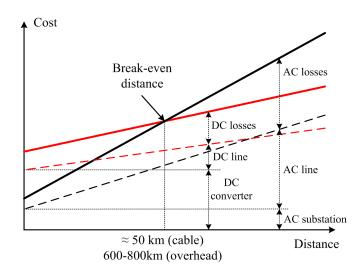

On the other hand, Desertec project is a global initiative to harness renewable energy from several regions in the world with current focus on Europe, the Middle East, and North Africa (see Figure 1.3). This stage is known for short as Desertec EU-MENA. The Middle East (ME) and North Africa (NA) are particularly characterized by an abundant solar energy resource. The ultimate goal is thus to build large scale solar and wind power stations in MENA region and develop a Euro-Mediterranean electricity network primarily made up of HVDC lines. The long term goals set by such large-scale projects contribute significantly to the drive for adequate generation and transmission technology, particularly HVDC technology.

Figure 1.3 The Desertec EU-MENA project to trade the North African and Middle Eastern renewable energy with Europe.

The world's first commercial HVDC line was the Gotland 1 project in Sweden which was commissioned in 1954 and employed mercury arc valves. The technology evolved quickly over the following two decades and as of the late 1970s, thyristor based line commutated converter (LCC) technology became the commercial standard for HVDC point-to-point projects. LCC technology – also known as HVDC Classic – is now a mature solution that has been predominantly used for transmitting power over long distances. Point-to-point transmission ratings of about 3 GW over long distances (>1000 km) with only one bipolar HVDC Classic dc line are state of the art. The technology has witnessed a further leap in voltage and power ratings with the world's first ±800 kV dc project built in China (Yunnan- Guangdong) having a

transmission rating of 5 GW [11]. As well, another  $\pm 800$  kV LCC HVDC link in China (Xiangjiaba – Shanghai) has been commissioned in 2010 with 6.4 GW rating [12]. Additional Chinese projects of 6–8 GW or possibly higher are in the planning stages.

Despite the maturity and reliability of LCC technology, it has the following shortcomings [6], [13]:

- Power flow is reversed by changing dc voltage polarity.

- Requires strong ac connection with a stiff ac voltage for proper operation (to avoid commutation failure)

- Large ac filters are required to filter ac current and meet converter's reactive power demand

- No decoupled active and reactive power control

For the above reasons, LCC is a less attractive technology for multi-terminal dc (MTDC) connections where several point-to-point HVDC links are interconnected.

### 1.2 Multi-terminal dc networks

Voltage-source converter (VSC) technology, on the other hand, offers an essential feature; power reversal is realized without reversing the dc voltage polarity. Thus, bidirectional power flow is possible electronically at fast power reversal rates. Additionally, VSC stations can provide black start as well as decoupled active and reactive power control for operation at unity power factor (or within a small range of power factor values) in steady state where relatively smaller filters are required to remove high order harmonics from the ac current waveforms. Therefore, the VSC multi-terminal HVDC grid is the core of academia and industry interests when looking beyond point-to-point connections [6], [8].

A major push to the commercial utilization of the VSC concept in modern HVDC systems is the development of a fully modular VSC concept, known as the modular multilevel converter (MMC) [14]. With its modular design, the MMC concept simplifies manufacturing and installation processes and, most significantly, it conceptually permits the scalability of the VSC concept to ultra-high voltage levels.

Unlike ac systems, voltage collapse in dc lines is very quick under dc faults. With the current-source based LCC technology, controllers are able to handle the fault condition before the dc current rises to destructive levels to the thyristors. Moreover, thyristors are advantageously characterized by a high surge current capability. This high surge capability is not available to state of the art IGBT/diode modules which form the building block of contemporary VSC technologies. Without additional circuitry, the VSC circuit is forced to an uncontrolled rectifier mode once the dc voltage dips and the semiconductor devices may be damaged by the uncontrollable high current rushing through freewheeling diodes into the dc side. The dc fault vulnerability of VSCs constitutes one major showstopper for MTDC networks realization to date.

As VSC vulnerable diodes cannot handle the fault current for more than a few milliseconds, dependence on ac-circuit breakers to trip the circuit is not suitable since they typically interrupt the fault current in 2-3 power frequency cycles. Several solutions have been proposed to address this problem for a point-to-point link. These can be classified into three generic concepts:

- 1. Diverting fault current into a bypass path until the fault is externally interrupted; typically by an ac side breaker;

- Injecting a sufficient reverse dc voltage in the dc circuit to quickly suppress dc current, or;

- 3. Triggering a controlled ac side fault so as to inhibit fault current infeed from the ac circuit.

The bypass concept is typically realized using bypass thyristors triggered to share the fault current with affected freewheeling diodes until the ac side breaker trips the circuit [15]. Although in industrial use (e.g. Trans Bay Cable project), this solution is not optimal particularly for overhead HVDC lines.

Injecting reverse dc voltage in the dc circuit can be administered by either more complex VSC structures (e.g., as in [16] and [17]) or by using a dc circuit breaker (DCCB) connected at the VSC dc side (e.g., as in [18] and [19]). Regardless of the technology used to build said DCCB, the latter will need to be significantly quicker

than mechanical ac circuit breakers and also be able to dissipate the energy stored in the dc circuit.

The third concept creates a controlled ac fault at the ac terminals of the VSC station to stop current infeed into the dc circuit under fault [20], [21].

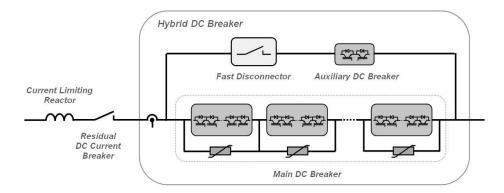

Analogous to ac grids, reliable dc networks must feature defined protection zones with high selectivity where all types of faults are rapidly isolated without affecting the rest of the system. Regardless of the protection arrangement for terminal VSC stations, dc circuit breakers are required at dc nodes (internal busbars) to interrupt high fault currents in the absence of zero current crossings. As previously mentioned, conventional ac mechanical circuit breakers are slow and suited to ac type faults. On the other hand, solid-state dc circuit breakers composed entirely from forced commutation semiconductor devices can achieve fast interruption times albeit at high capital cost and on-state operational losses [19]. As a compromise a hybrid dc circuit breaker has been proposed where a mechanical path serves as a main conduction path with minimal losses during normal operation, and a parallel connected solid-state breaker is used for dc fault isolation [18]. However, capital cost remains high, and it has relatively large footprint. The mechanical opening time is a few milliseconds at 320kV [22]. Also, the semiconductors conduct and commutate high fault currents arising during the mechanical path opening time.

It can thus be concluded that there is no efficient solution to the dc fault protection in an MTDC network to date. As research and development is underway, the most satisfactory solution seems to be a fast mechanical dc circuit breaker that is capable of interrupting the circuit in less than 2ms. While this is a very stringent requirement from a mechanical assembly, it might be eventually achieved in the coming one or two decades given the substantial effort and investment dedicated to developing such a mechanical breaker.

In addition to effective protection in faulty conditions, voltage regulation and optimized power flows through network lines are also mandatory for proper and efficient operation of a dc grid. Dual to frequency in an ac network, a stable dc voltage level is the indicator to power balance along the dc system. It follows that subtle dc voltage control schemes must be developed and utilized. Several techniques have already been devised [23]. However, most of these techniques are not suitable for generic dc grids with large numbers of converters and dc nodes.

A real dc super-grid with multiple in-feed points, tapping points, and various terminals connected to different ac grids renders the voltage regulation issue even more complex. Forming and solving an optimal dc load flow problem may be a practical solution to calculate terminal voltage set points. Information and commands throughout the network can be exchanged between individual dc nodes and a control center, which determines optimal load flow scenarios similar to ac systems [24].

### **1.3** Motivation and objectives

In general, any attempt to address voltage regulation in a real dc grid cannot disregard that it is not possible to build a vast grid without voltage stepping and matching. Unlike an ac transformer, so called 'dc transformer' will be based on active controlled power electronic components where dc voltage control and/or power flow control can be readily augmented. Having grid components dispersed through the DC network actively contributing to voltage regulation, power flow control and rapid fault protection, in addition to terminal ports, will significantly boost network controllability and security.

While organizations such as CIGRE, IEEE, and IEC are developing guidelines and standards for common HVDC manufacturing and operation practices, more point-to-point links are planned and commissioned in the absence of common standards [25]. The result is more point-to-point connections at different voltage levels (*e.g.*  $\pm$ 80kV,  $\pm$ 150kV and  $\pm$ 320kV), technology, and topology concepts. Therefore, apart from any efficiency considerations, high power dc-dc converters (dc transformers) appear the only way to interconnect and retrofit existing point-to-point links.

When dc transformers built with active components are present at vital nodes throughout a potential dc grid, an augmented fault protection function will constitute a milestone towards a super-grid. It is, therefore, a motivation of this research to explore the possibilities of dc fault isolation being administered by dc transformers at dc nodes. In light of the above discussion, the thesis primary objectives are:

- Reviewing state of the art dc-dc power electronics converter topologies and identifying main challenges impeding their utilization in high voltage and high power applications.

- Identifying a set of desirable features in candidate dc-dc power electronic converters for use in multi-terminal HVDC networks.

- Proposing and analysing a quasi-two level mode of operation for the modular multilevel converter as the kernel of an isolated dc-dc converter topology suitable for high voltage and high power applications

- Proposing and analysing a family of hybrid multilevel dc/ac converter topologies that utilizes said new mode of operation.

- Holding a thorough comparison between the considered topologies in terms of conduction losses, installed power electronics, soft switching characteristics, energy storage, and filtering requirements.

- Analysing the use of the proposed dc/ac converter topologies as the kernel of a non-isolated dc-dc converter topology and assessing its viability for high voltage and high power applications

- Provide conclusions as well as recommendations for future extension of the research undertaken in this thesis.

# Chapter 2

### **DC-DC** Converters for DC networks

This chapter reviews various dc-dc converter topologies and their building blocks with emphasis on their merit for high voltage and high power applications. The basic hard-switched dc-dc converters will be revisited. Basic dc/ac bridge structures suitable for so-called front-to-front or direct dc-dc converter topologies will be presented. A review of isolated and non-isolated dc-dc converter topologies will be conducted with emphasis on topologies of promise for HVDC. This chapter will conclude with a set of desirable features in any potential dc-dc converter for HVDC applications. This set of desirable features will be used in subsequent chapters to evaluate the new structures proposed in this thesis.

#### 2.1 Hard switched DC-DC converters

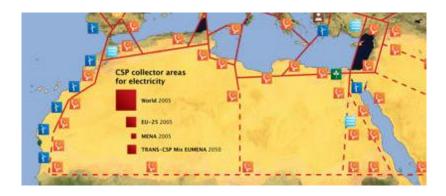

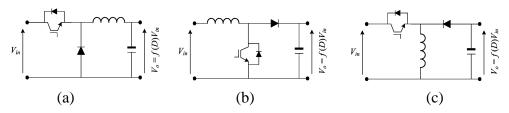

Numerous designs of hard-switched dc-dc converters can be found in the literature [26]. Figure 2.1 depicts a three-port generic representation of non-isolated hard-switched dc-dc converter structures. In Figure 2.1, D is the switch on-state duty ratio,  $V_{in}$  is input voltage, and  $V_o$  and  $V_o$ ' are output voltages. For the basic buck converter, f(D) = D. For the basic boost converter, f(D) = 1/(1 - D). For a basic buck-boost converter, f(D) = -D/(1 - D).

Figure 2.1 Generic three-port dc-dc converter representation

The three basic converters are shown in Figure 2.2. Further details as to their design and operation can be found in many sources (for instance, [27]) and it is not the focus of the current discussion. The key aspects of interest for the present discussion are the switching frequency, passive components design, and semiconductors blocking voltages. With higher voltage and power levels, it is desirable to minimize the size of the passive components (inductors and input and output capacitors). It is therefore desirable to increase the switching frequency. As a direct consequence, switching losses rise given the hard switching<sup>1</sup> nature of power electronic switches.

On the other hand, the blocking voltage of power electronic components is  $V_{in}$  for the buck converter,  $V_o$  for the boost converter, and  $V_{in} + |V_o|$  for the buck-boost converter. It follows that to scale these designs to higher voltages, series connection of active switching devices is necessary. Series connection of insulated gate bipolar transistors (IGBTs), for instance, is a demanding task that requires complex gate drives and snubber circuits to account for the non-uniform gating delays and enforce static and dynamic voltage sharing.

This discussion points to the apparent demerit of basic non-isolated hard-switched dc-dc converter designs beyond low voltage applications.

Figure 2.2 Basic dc-dc converter designs: (a) buck, (b), boost, and (c) buck-boost.

### 2.2 DC/AC bridge designs

DC/AC voltage source converter bridges are the building blocks of the isolated and non-isolated dc-dc converters reviewed in section 2.3 and section 2.4. Therefore, an understanding of their operating principles is essential. This section outlines relevant aspects in terms of their operation and control.

<sup>&</sup>lt;sup>1</sup> A power electronic switch is hard switched when it truns on or off with current flow therein.

#### 2.2.1 The two-level voltage source converters

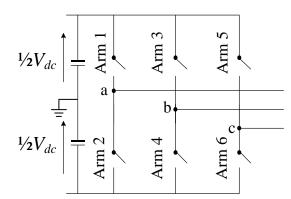

The three-phase two-level VSC topology is shown schematically in Figure 2.3. Each phase leg hosts two semiconductor switches (or two series-connected switch arrays) which conduct complementarily with an intervening dead-time. During the dead time, both switches are gated off. Three phase alternating voltages can be produced at the three ac poles. The voltage of each ac pole with respect to dc link midpoint is one phase voltage. With a constant dc voltage, the alternating phase voltage at each ac pole is a square wave. Therefore it cannot be operated in 180° modulation when interfaced directly to electric grids and more sophisticated modulation techniques are needed. Two-level VSC modulation techniques have been intensively researched with three primary targets in mind: mitigating harmonic distortion in the VSC ac voltages and currents, improving dc link utilization, and minimize switching losses.

Figure 2.3 A two-level three phase voltage source converter

Generally, sinusoidal pulse width modulation (SPWM) generates a train of pulses with a voltage-second area the same as that of the reference signal over one switching or fundamental cycle [28]. Its downside is that the maximum linear modulation index is limited to 1pu beyond which non-linear over-modulation occurs and additional low order harmonics are generated in the output. Furthermore, the semiconductor devices are switched at the carrier frequency. This leads to significant switching losses given the carrier frequency should be significantly higher than the fundamental voltage (in the kHz range).

SPWM with triplen or third harmonic injection extends the maximum modulation index to 1.155pu with all other SPWM features retained. The triplen voltage components in the output voltage cancel in the line-to-line voltages and thus do not appear in the load currents.

Space vector modulation (SVM) is developed from the space vector representation of the inverter output voltage in the  $\alpha$ - $\beta$  plane. The dc voltage utilization is 1.155pu, and it offers additional flexibility in terms of pulse placement and switching patterns selection, hence switching losses can be optimized. SVM is suitable for real-time and digital implementation, but it assumes a perfect three phase grid/load in terms of phase and magnitude [28].

Selective harmonic elimination (SHE) is another modulation technique that controls the fundamental voltage and eliminates specific harmonics by directly calculating the switching instances. In this manner, it generates high quality output voltage at a lower switching frequency than other modulation methods. It also enables the VSC to operate at a relatively high modulation index (exceeding 1.155pu) as achievable in three-phase systems.

#### 2.2.2 Multilevel voltage source converters

Two level VSCs traditionally suffer from EMI problems due to the high dv/dt at medium voltages (or even low voltages above a few hundreds of volts). Multilevel converter structures have been introduced to mitigate this problem by introducing additional levels in the output voltage. This also improves the total harmonic distortion (THD) figure in the output voltage and simplifies the connection series semiconductor devices to block the dc voltage as required in medium voltage applications (e.g., variable speed drives).

A group of multilevel converters is based on the clamping technique. An example of clamped converters is the diode clamped multilevel converter (DCMC) depicted in Figure 2.4a and the flying capacitor multilevel converter (FCMC) shown in Figure

2.4b [29]. The three-level DCMC, also called the neutral point clamped (NPC) converter, was proposed in 1981 [30] and later extended to general multilevel cases in 1983 [31]. Then, the flying capacitor multilevel converter was introduced in [32]. Several other topologies have been derived over the years from the basic DCMC and FCMC concepts. Examples of these topologies are; the active neutral point clamped (ANPC) converter [33], hybrid clamped multilevel converter (HCMC) [34], and the multilevel-clamped multilevel converter (MLC<sup>2</sup>) [35].

Figure 2.4 (a) Schematic of the diode clamped converter, and (b) a schematic of the flying capacitor inverter.

On the downside, these topologies become complex in terms of power circuit and modulation when the voltage level number is increased. Additionally, the power switching device losses are not evenly distributed among the switches in each arm, which challenges loss analysis and thermal design.

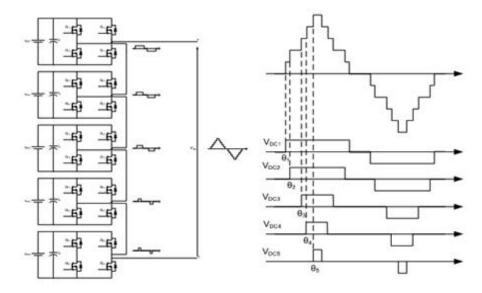

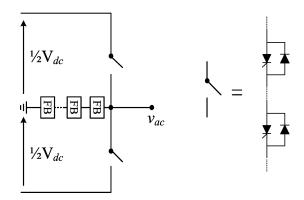

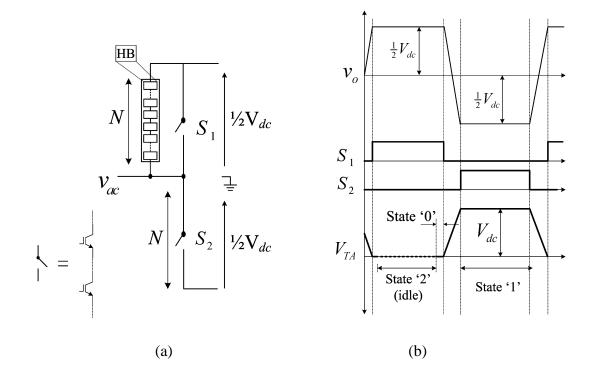

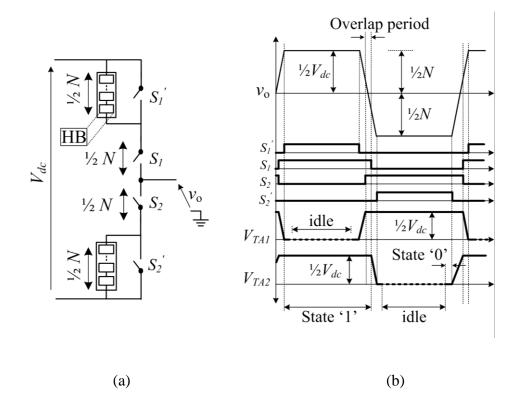

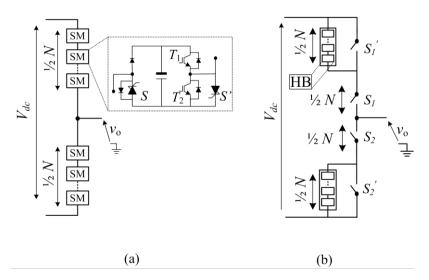

To provide high number of voltage levels in the output, the cascaded full-bridge converter was introduced. It was a significant step towards enhanced modularity of industrial converters offering simplicity of the power circuit and control design. As shown in Figure 2.5, several full-bridge converter modules are cascaded in each phase and are modulated such that each module produces a voltage level of certain

duty ratio so as to synthesize a low-THD phase voltage waveform. The primary drawback of the cascaded full-bridge converter is the requirement of a separate dc source for each module. These dc sources can be photovoltaic panels or batteries which is complex to arrange in a real industrial environment [36]. The challenge of using the cascaded-full-bridge converter concept with a common dc-link has been solved with the introduction of the modular multilevel converter concept in 2001 [37].

Figure 2.5 Structure and waveforms of an 11-level cascaded full bridge multilevel converter.

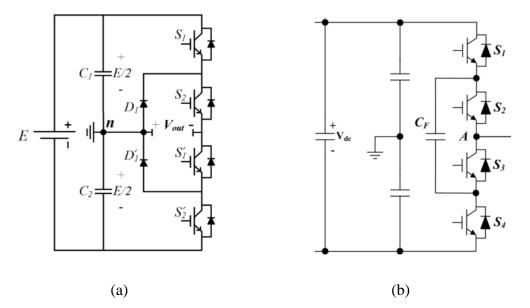

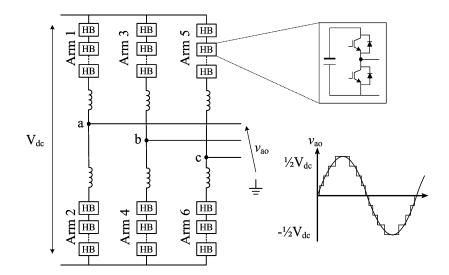

#### 2.2.3 The modular multilevel converter (MMC)

The arm of each phase leg in an MMC comprises typically a cascade connection of half-bridge VSC chopper cells (HB cells) connected in series with an arm inductor as in Figure 2.6. The MMC was first introduced in 2001 [38] and features the following merits [39]:

- Distributed capacitive energy storages rather than a concentrated dc link capacitor;

- Modular design which facilitates manufacturing, assembly, and maintenance;

- Redundancy is possible in a simple manner as well as scaling to high voltages by series connection of HB cells;

- Low total harmonic distortion in the ac output.

- Grid connection via standard transformer or transformerless; and

- Possibility of common dc bus configurations for multi-drive and high-power applications.

Figure 2.6 Generic Structure of the modular multilevel converter.

On the down side, the converter requires a higher number of semiconductors and gate units (e.g., with respect to the two-level VSC). The total stored energy of the distributed capacitors is significantly higher than that of a conventional 2L-VSC or NPC-VSC, which reflects on bridge volume.

#### 2.2.3.1 MMC operation

Conventionally, established modulation techniques operate the MMC such that the upper and lower arms of the same phase-leg conduct simultaneously, and this constitutes the sum of the cell capacitor voltages in conduction path of both arms must be equal to the total DC link voltage minus the AC voltage drop in the arm

inductances [40]. This necessitates the voltages developed across the cell capacitors of the upper and lower arms to be complementary, which can be approximated by;

$$v_{uj} = \frac{1}{2} V_{dc} \left( 1 - m \sin(\omega_s t + \varphi_j) \right)$$

$$v_{li} = \frac{1}{2} V_{dc} \left( 1 + m \sin(\omega_s t + \varphi_j) \right)$$

(2.1)

where  $V_{dc}$ ,  $v_{uj}$ , and  $v_{lj}$  are the converter input dc link voltage, upper arm voltage, and lower arm voltage, respectively; j representing phase a, b, or c, m being the modulation index, and  $\varphi_j = \{0, \frac{4}{3}\pi, \frac{2}{3}\pi\}$  for the three phases a, b, and c, respectively. With the arm voltages in (2.1), the ac pole voltage is a staircase sinusoidal output of peak magnitude  $\pm \frac{1}{2}V_{dc}$ . Thus minimal harmonic content is present in the ac pole voltage and no ac filters are required should the number of steps be sufficient [37], [41].

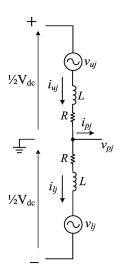

With such simultaneous operation of the upper and lower arms of each MMC phase leg, the arm currents of each phase-leg contain ac and dc components. With reference to the equivalent circuit of Figure 2.7, the upper and lower arms currents of one phase leg can be expressed as in (2.2) and (2.3).

Figure 2.7 The equivalent circuit of one MMC phase leg.

$$i_{uj} = \frac{1}{2}i_{pj} + i_{CMj}$$

$$i_{lj} = i_{CMj} - \frac{1}{2}i_{pj}$$

(2.2)

where;

$$i_{pj} = I_{pj} \sin(\omega_s t - \varphi_{ij})$$

(2.3)

$\varphi_{ij}$  being the current phase angle in each ac pole and  $I_{pj}$  the peak phase current. The fundamental frequency ac component of the arm current ( $\frac{1}{2}i_{pj}$ ) represents the fundamental current that is associated with active power exchange between the converter and the ac side. In (2.2),  $i_{CM}$  represents the common mode current component of the arm current which represents the power exchange between the converter and the dc side. It also contains a number of low-order harmonics (predominantly 2<sup>nd</sup> harmonic) that are caused by cell capacitor voltage fluctuations in attempting to counter the ac voltage drop in the arm inductances. The sum of even order harmonic arm currents is also called the circulating current. The sum of circulating currents in all phase legs is zero. This implies the circulating currents are decoupled from the ac and dc circuits and flow only within the MMC circuit.  $i_{CMj}$  can be expressed as in (2.4) [42] [41].

$$i_{CM} = \frac{1}{3}I_{dc} + I_{2j}\sin(2\omega_s t - \varphi_{2j})$$

(2.4)

where  $I_{dc}$ ,  $I_{2j}$ , and  $\varphi_{2j}$  are the dc common mode current component, peak 2<sup>nd</sup> harmonic current, and 2<sup>nd</sup> harmonic current phase angle in each phase, respectively. The loop equations of the MMC phase leg in Figure 2.7 are;

$$L\frac{di_{uj}}{dt} + Ri_{uj} + v_{pj} + v_{uj} = \frac{1}{2}V_{dc}$$

(2.5)

$$L\frac{di_{lj}}{dt} + Ri_{lj} - v_{pj} + v_{lj} = \frac{1}{2}V_{dc}$$

(2.6)

Summing (2.5) and (2.6) yields (2.7).

$$v_{diff-j} = L \frac{d}{dt} (i_{uj} + i_{lj}) + R (i_{uj} + i_{lj}) = V_{dc} - (v_{uj} + v_{lj})$$

(2.7)

Using (2.2), (2.7) evolves to

$$v_{diff-j} = 2\left(L\frac{d}{dt}i_{CMj} + Ri_{CMj}\right) = V_{dc} - \left(v_{uj} + v_{lj}\right)$$

(2.8)

where  $v_{diff-j}$  is the voltage difference between the dc side and the phase leg voltage. From (2.8) the voltage  $v_{diff-j}$  can be used to control the common mode current  $i_{CMj}$  by controlling the energy exchange in the phase leg so as to suppress or minimize the circulating current component.

Assuming the number of cell capacitors inserted in the conduction path at any instant in the upper and lower arms are  $N_{uj}$ ' and  $N_{lj}$ ', respectively, the common mode current  $i_{CMj}$  can be expressed in terms of the upper arm voltage  $v_{uj}$  and the lower arm voltage  $v_{lj}$  as in (2.9) – (2.11) [43].

$$i_{uj} = \frac{N_{uj}}{N} C_{cell} \frac{dv_{uj}}{dt} , \quad i_{lj} = \frac{N_{lj}}{N} C_{cell} \frac{dv_{lj}}{dt}$$

(2.9)

Substituting (2.2) into (2.9), the latter can be rewritten as in (2.10);

$$\frac{dv_{uj}}{dt} = \frac{Ni_{CMj}}{N_{uj}C_{cell}} + \frac{Ni_{pj}}{2N_{uj}C_{cell}}$$

$$\frac{dv_{lj}}{dt} = \frac{Ni_{CMj}}{N_{lj}C_{cell}} - \frac{Ni_{pj}}{2N_{lj}C_{cell}}$$

(2.10)

Also, the common mode current loop equation is;

$$\frac{di_{CMj}}{dt} = \frac{R}{L}i_{CMj} + \frac{1}{2L}\left(v_{uj} + v_{lj} - V_{dc}\right)$$

(2.11)

Equations (2.10) and (2.11) form the set of differential equations of (2.12) and (2.13) which can be used to design suitable controllers to suppress the circulating current in

the phase leg. Circulating current suppression control loops have been developed and verified in several papers (e.g. [44] and [45]).

$$\int_{x}^{o} Ax + Bu \tag{2.12}$$

where;

$$x = \begin{bmatrix} i_{CMj} \\ v_{uj} \\ v_{lj} \end{bmatrix} , \quad A = \begin{bmatrix} \frac{R}{L} & \frac{1}{2L} & \frac{1}{2L} \\ \frac{N}{N_{uj}C_{cell}} & 0 & 0 \\ \frac{N}{N_{lj}C_{cell}} & 0 & 0 \end{bmatrix}$$

$$B = \begin{bmatrix} -\frac{1}{2L} & 0 & 0 \\ 0 & \frac{N}{2N_{uj}C_{cell}} & 0 \\ 0 & -\frac{N}{2N_{lj}C_{cell}} & 0 \end{bmatrix} , \quad u = \begin{bmatrix} V_{dc} \\ i_{pj} \\ 0 \end{bmatrix}$$

(2.13)

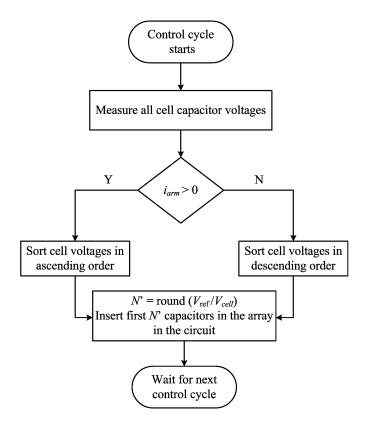

In steady-state, the converter power exchange with the ac side equals the power exchanged with the dc side. Under such a condition, the converter cell capacitors exchange zero net active power with the ac side over one or several fundamental cycles. However, the capacitors energies in each arm need to be balanced so that their voltages are maintained within a certain band around the desired set point  $V_{dc}/N$ .

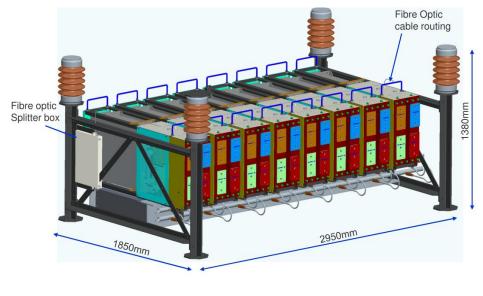

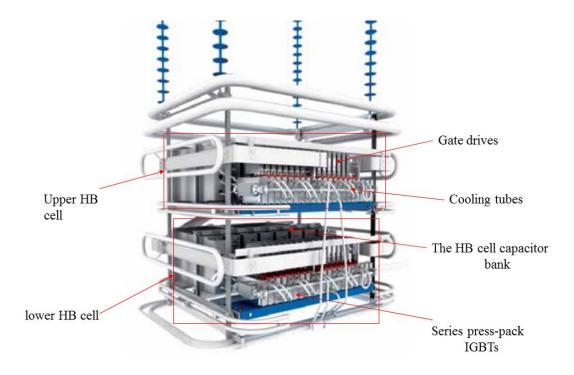

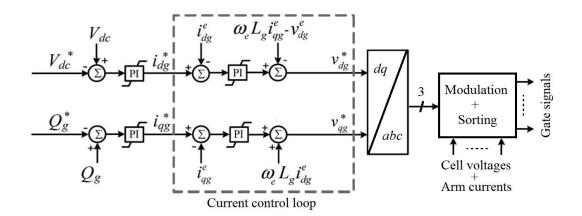

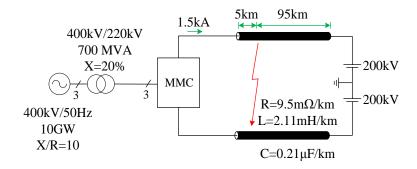

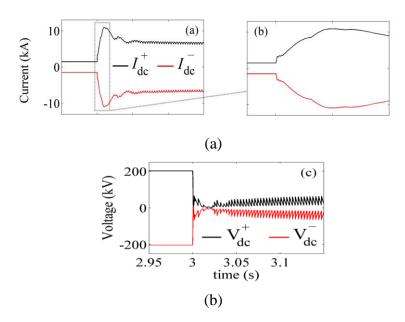

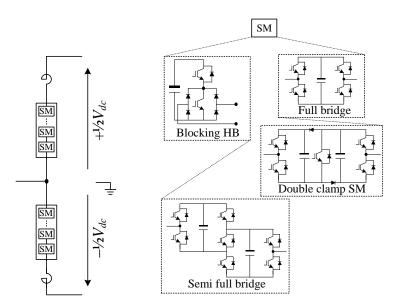

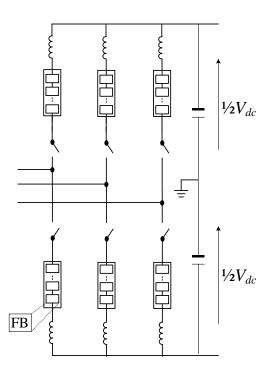

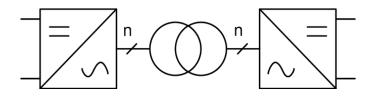

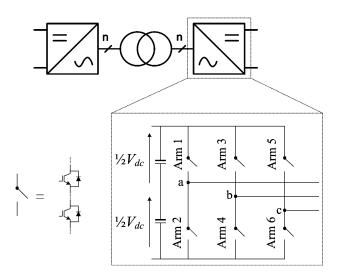

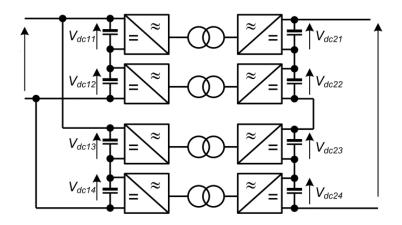

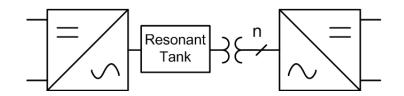

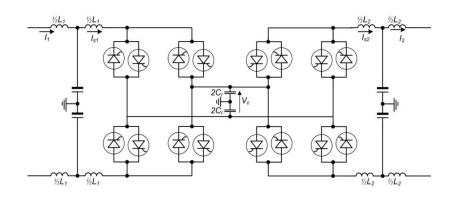

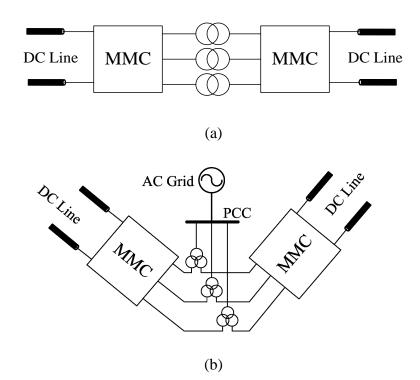

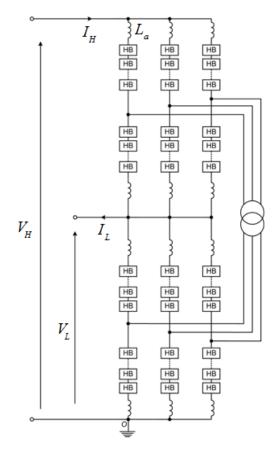

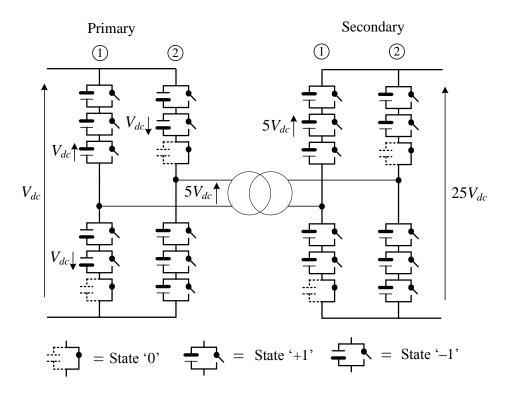

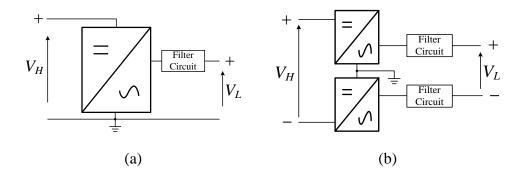

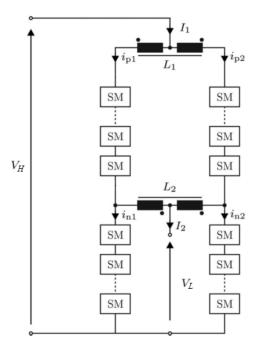

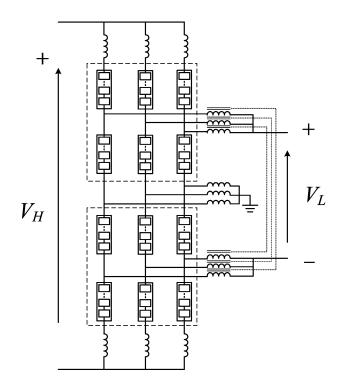

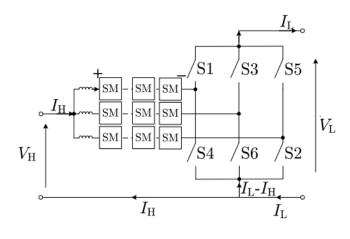

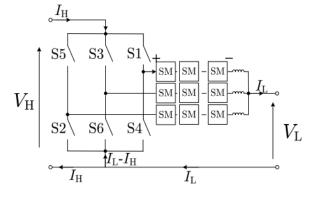

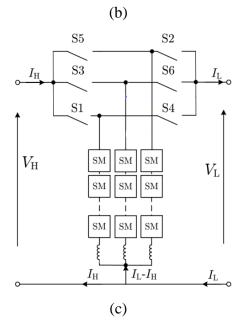

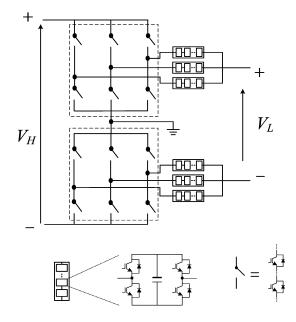

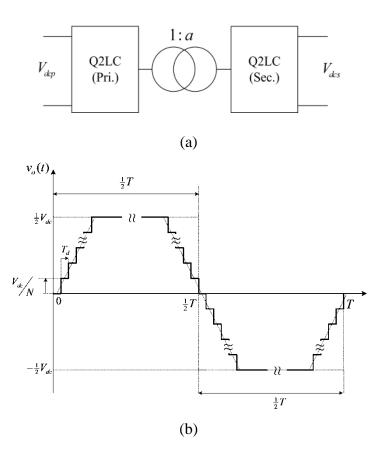

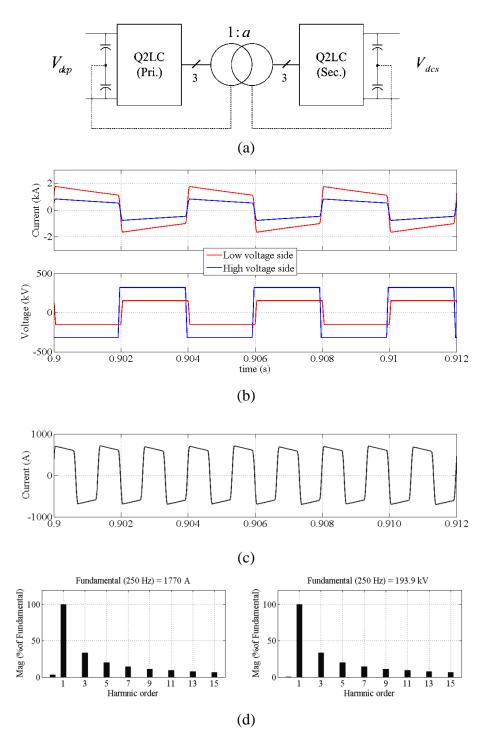

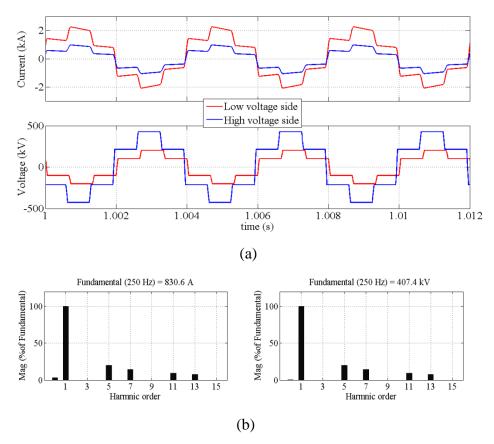

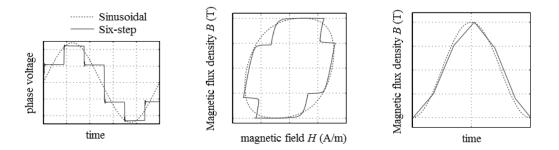

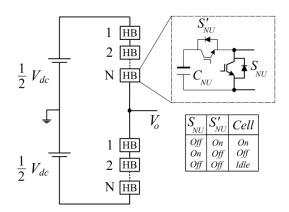

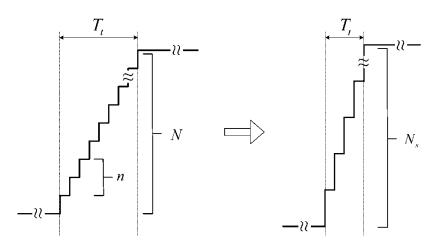

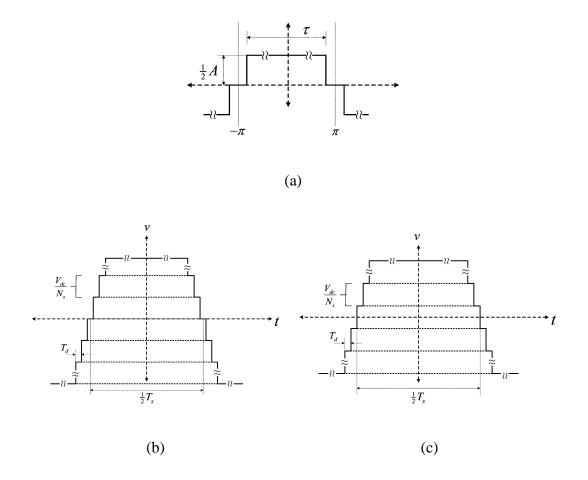

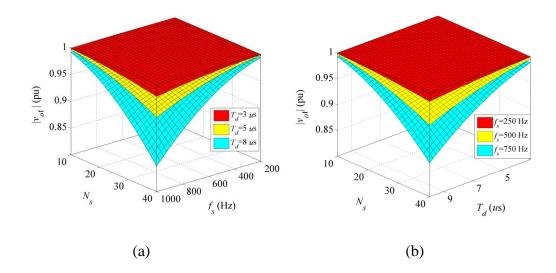

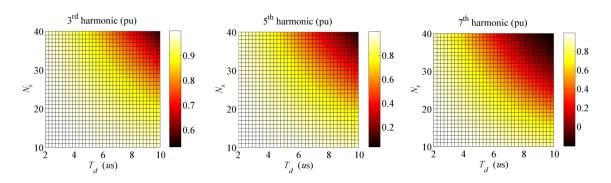

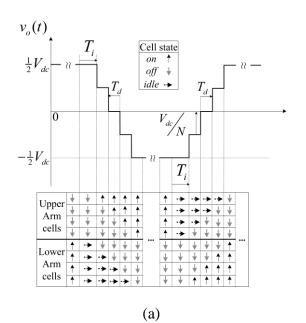

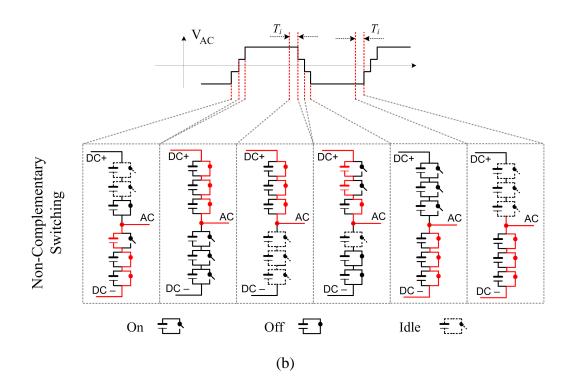

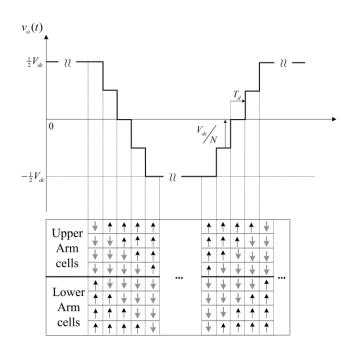

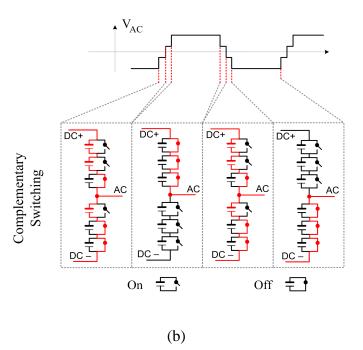

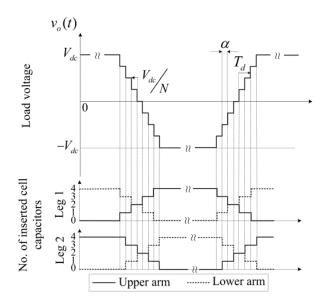

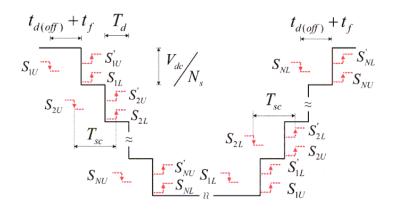

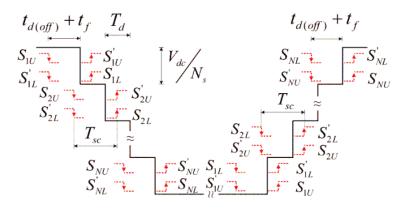

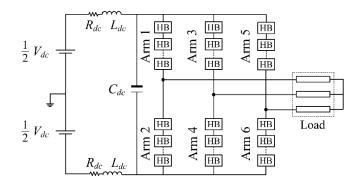

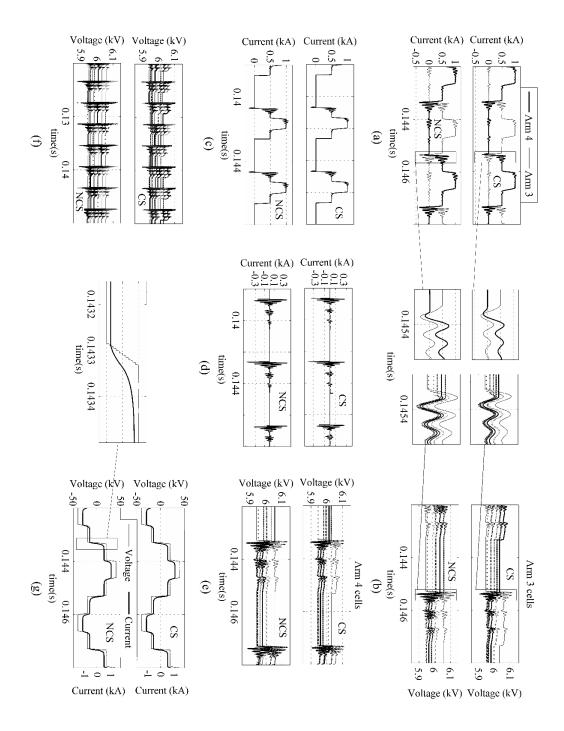

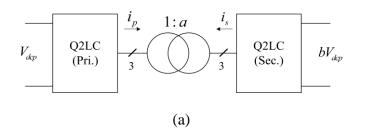

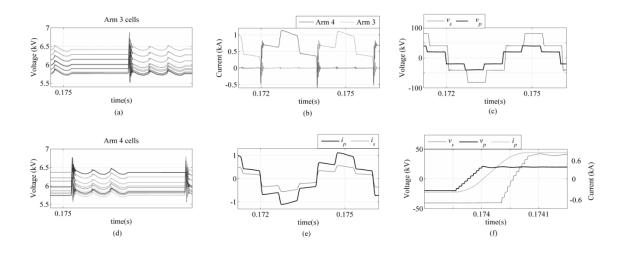

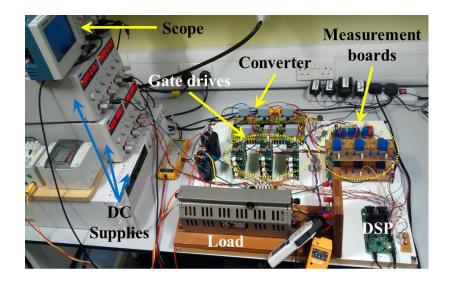

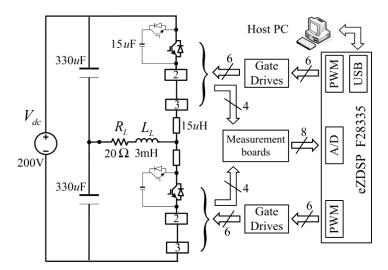

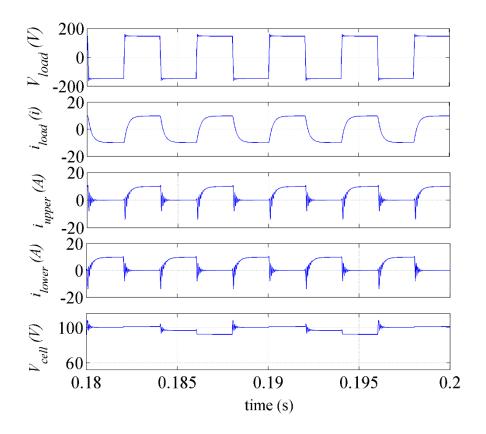

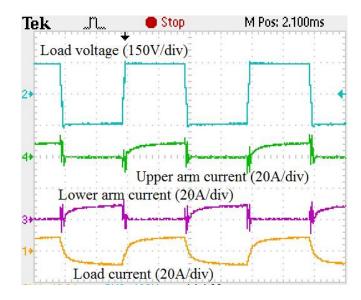

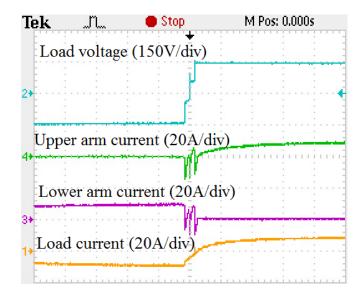

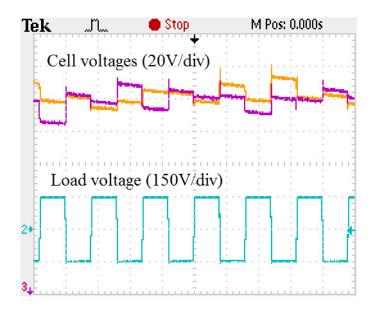

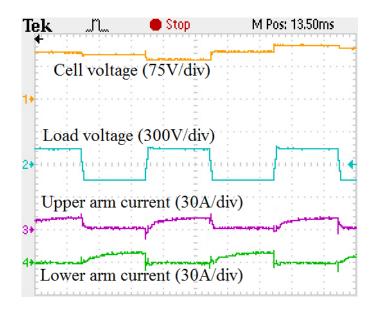

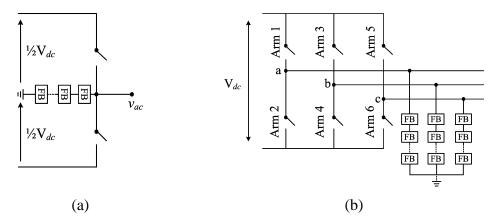

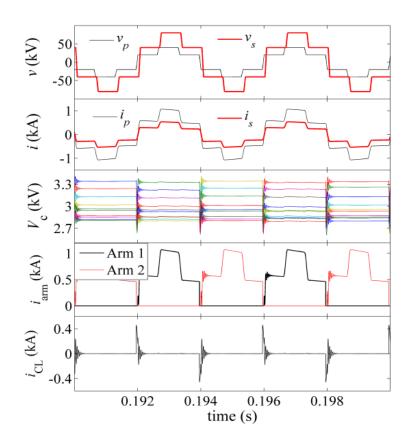

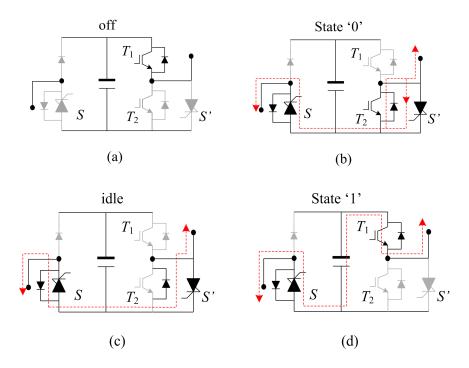

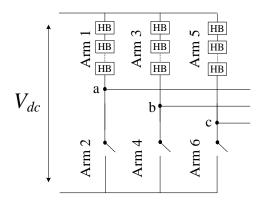

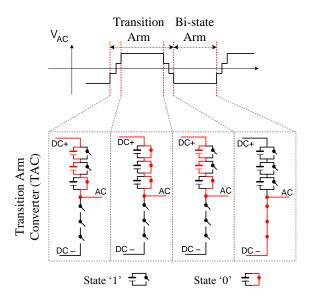

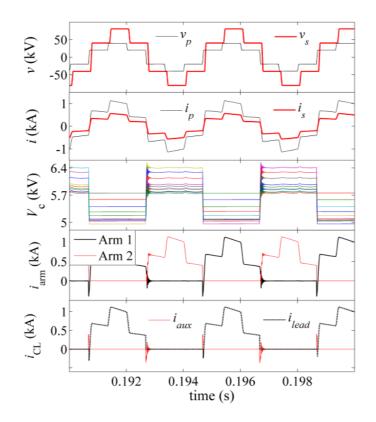

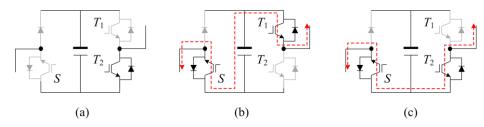

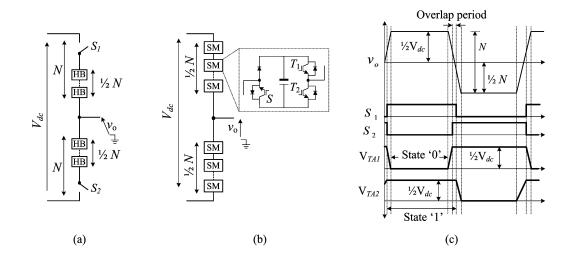

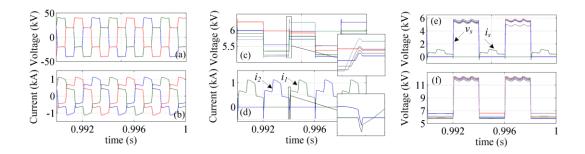

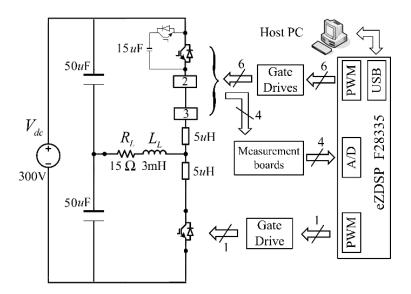

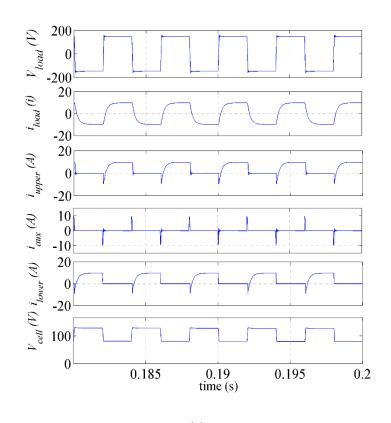

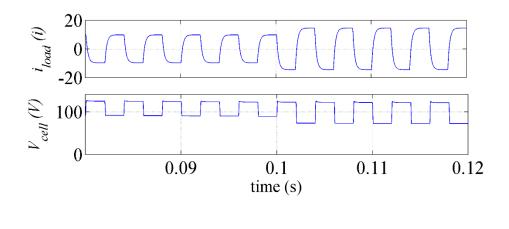

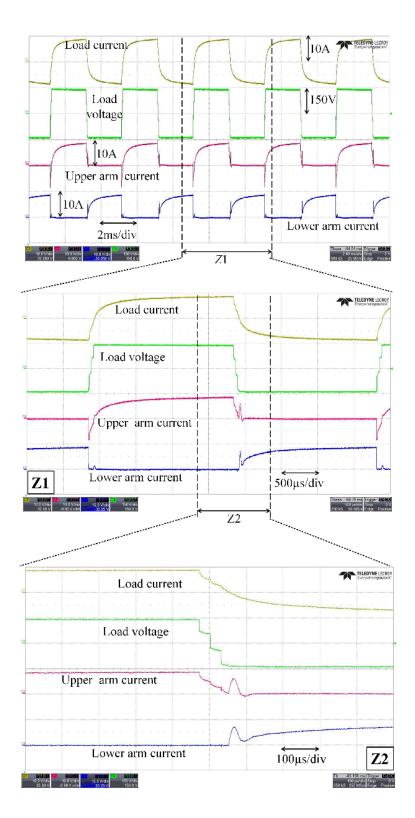

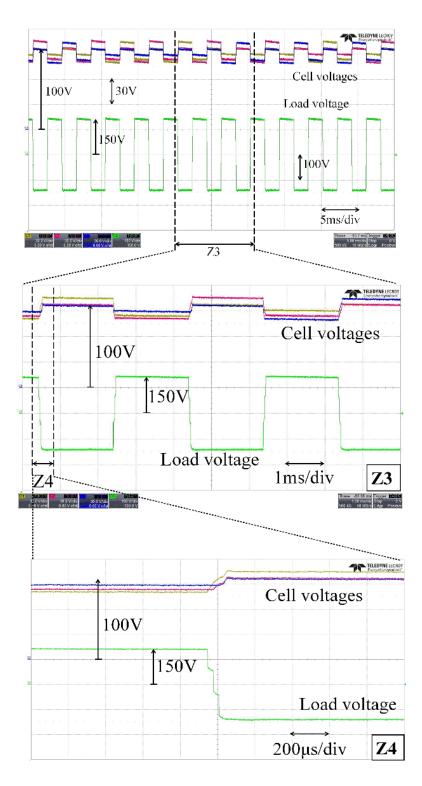

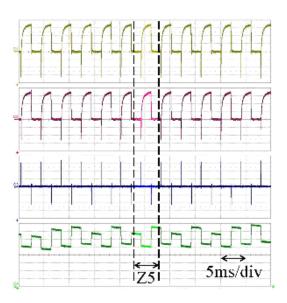

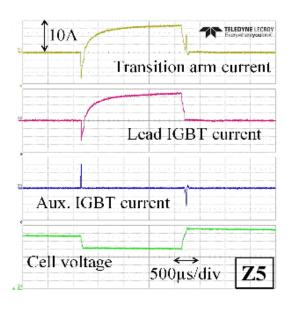

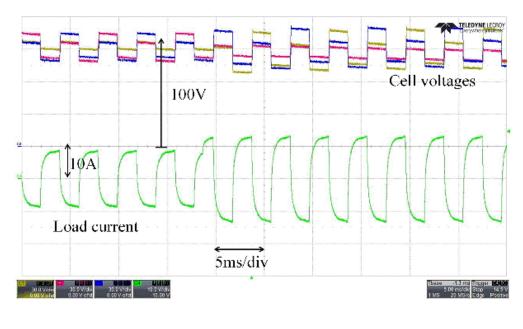

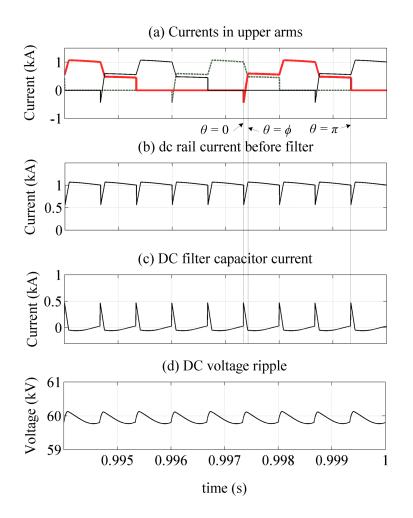

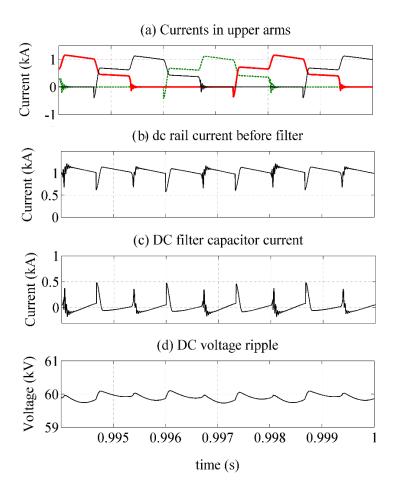

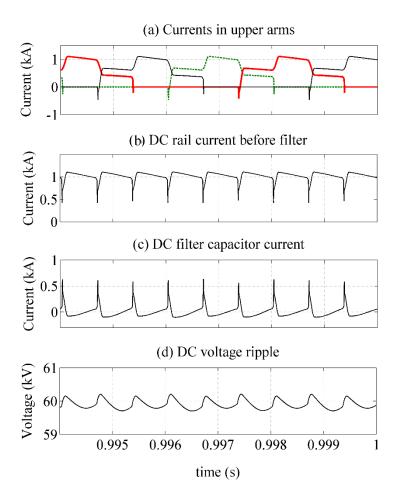

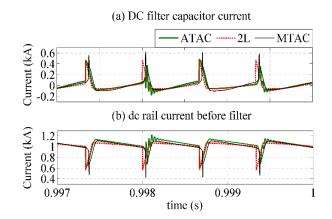

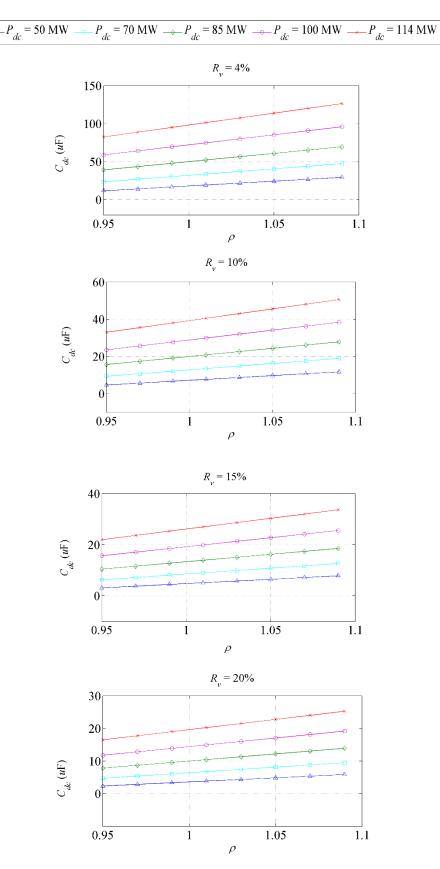

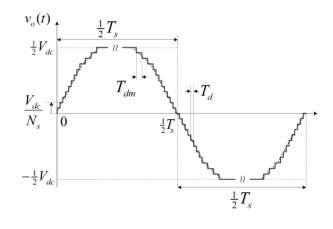

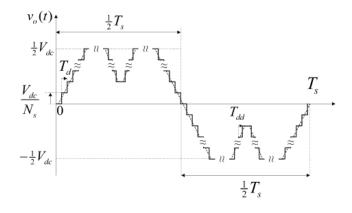

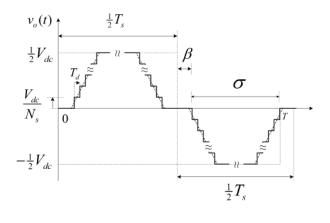

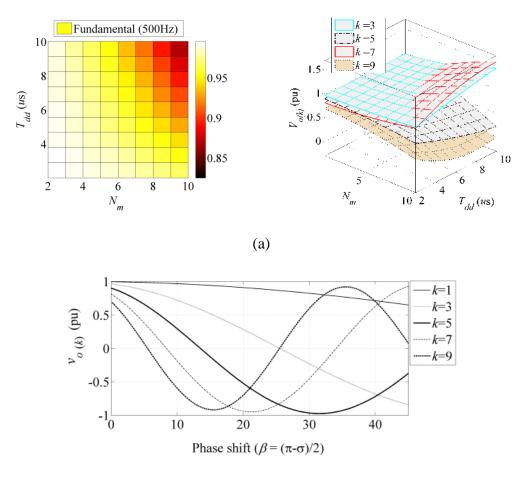

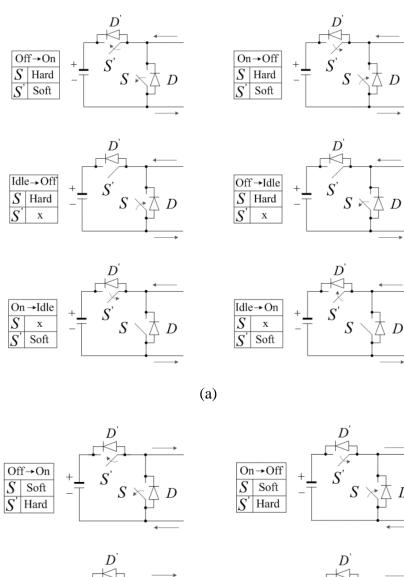

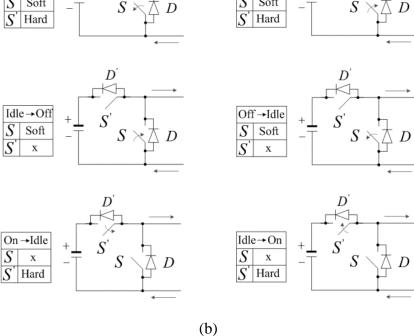

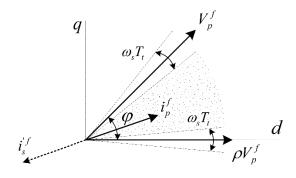

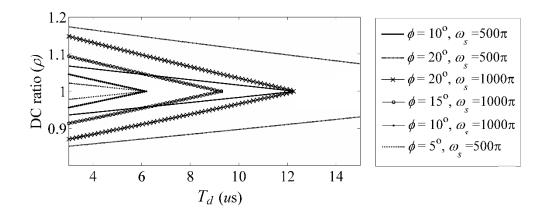

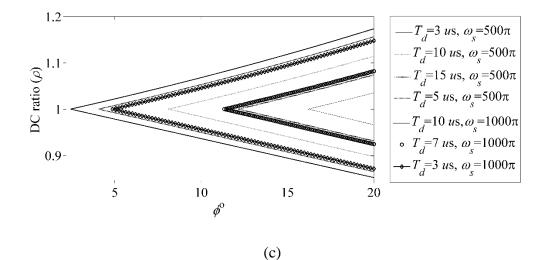

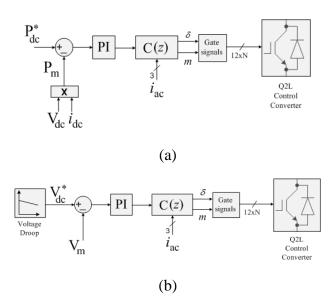

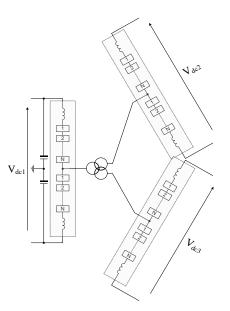

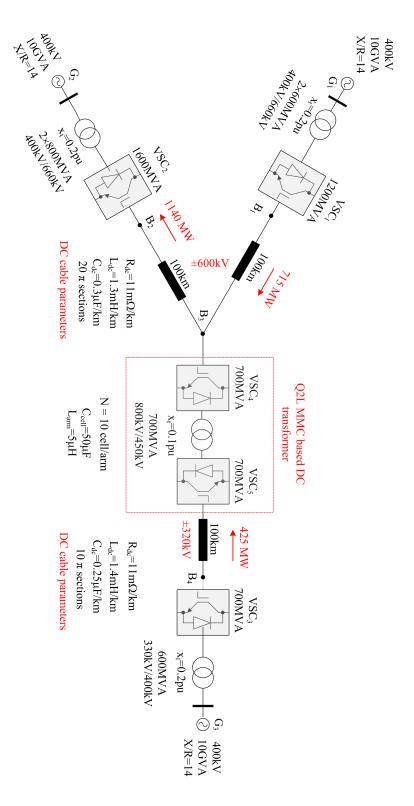

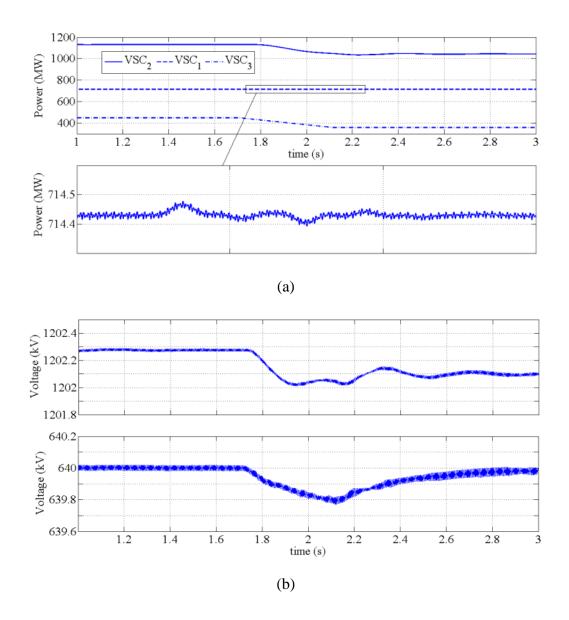

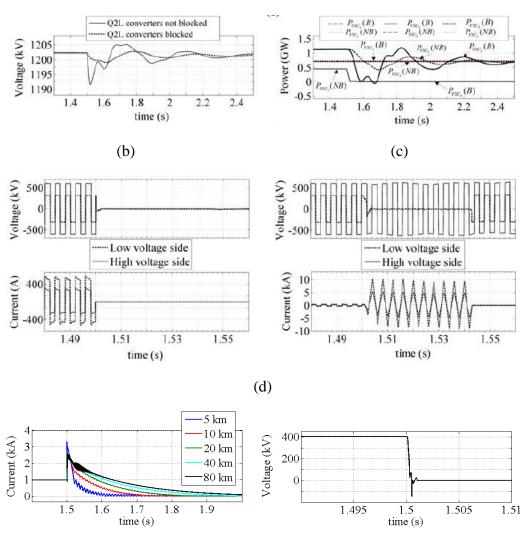

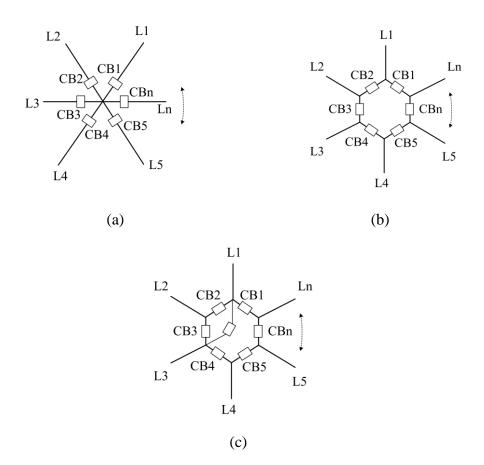

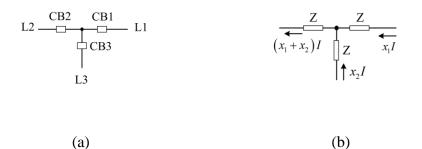

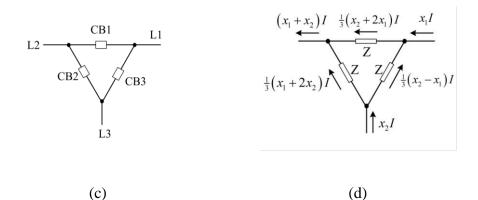

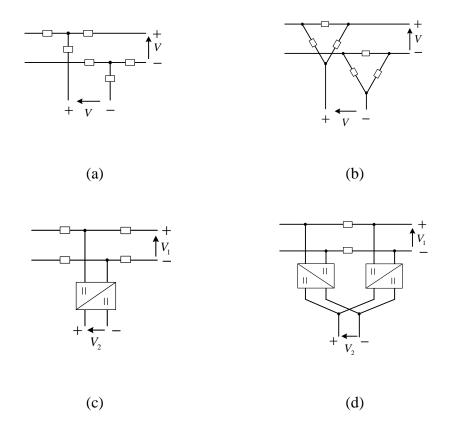

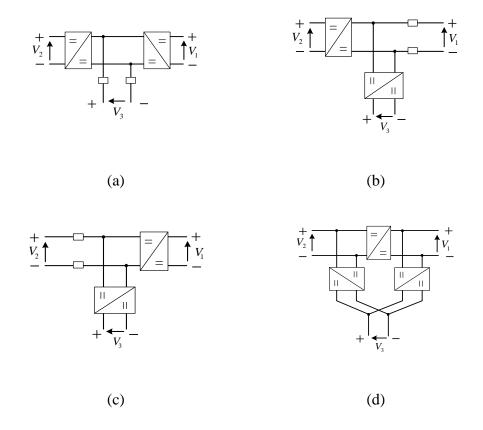

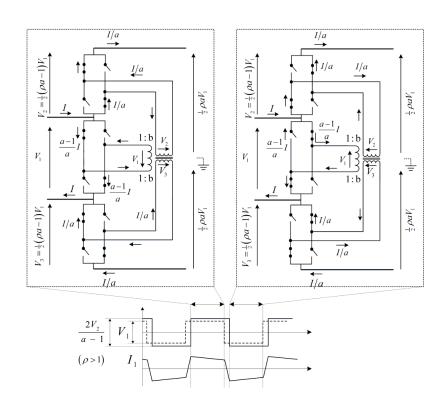

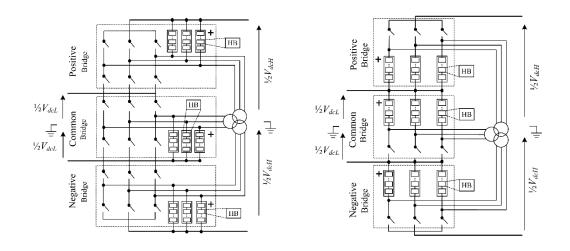

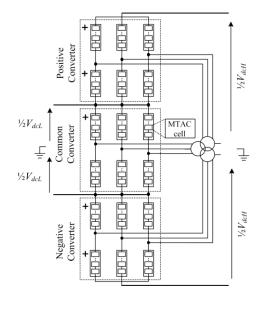

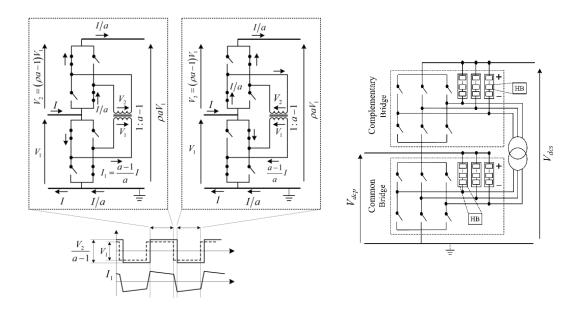

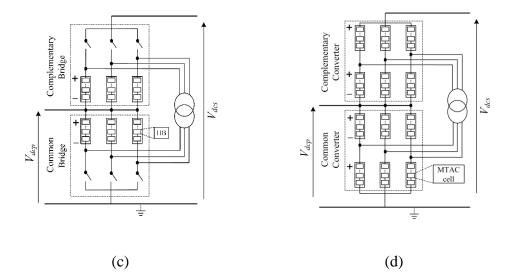

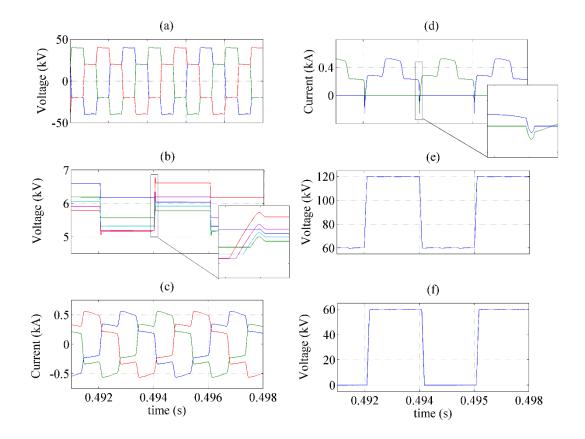

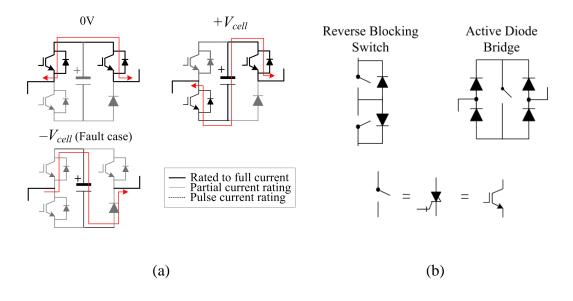

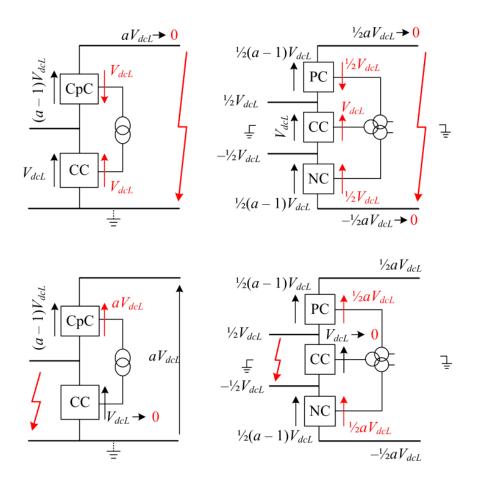

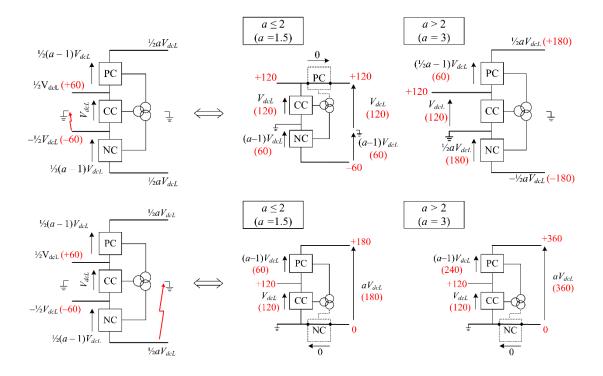

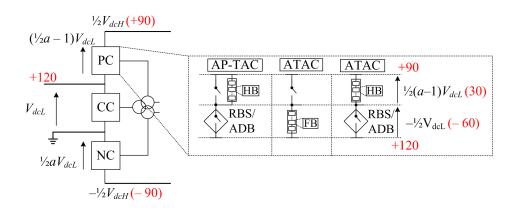

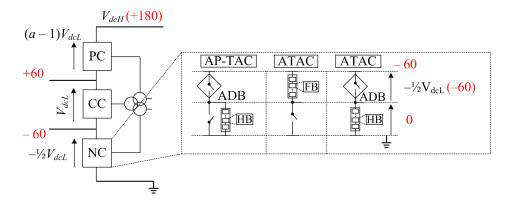

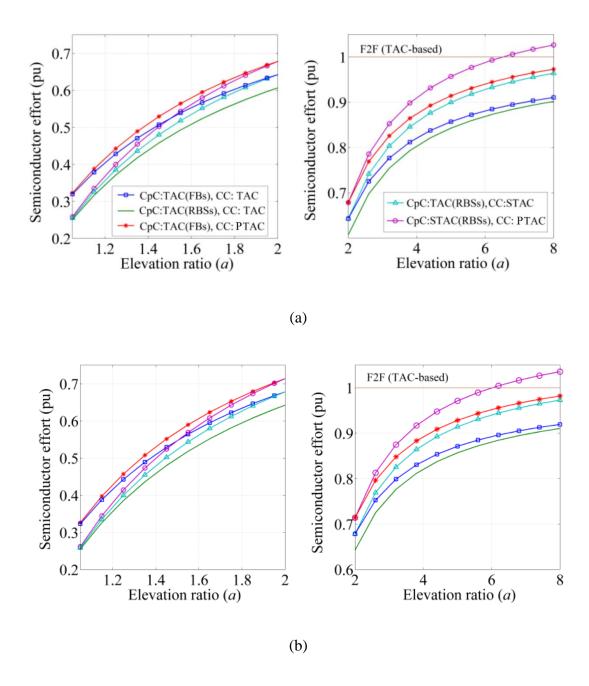

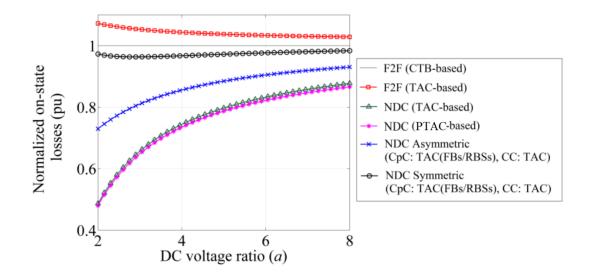

Several modulation and balancing methods have been proposed to achieve cell voltage balancing with minimal switching and control effort based on level-shifted PWM (e.g., [39], [41], [46]) phase-shifted PWM (e.g., [47], [48], [49]), selective harmonic elimination (SHE) [50]. But the simplest of these particularly for high number of output levels is the so called nearest level control (NLC) [51]–[52].