# Novel methods for enhancing accuracy and stability of Power Hardware-In-the-Loop simulations

Efren Guillo Sansano

Department of Electronic and Electrical Engineering University of Strathclyde

> A thesis submitted for the degree of Doctor of Philosophy

> > October 2018

#### Declaration

This thesis is the result of the author's original research. It has been composed by the author and has not been previously submitted for examination which has led to the award of a degree.

The copyright of this thesis belongs to the author under the terms of the United Kingdom Copyright Acts as qualified by University of Strathclyde Regulation 3.50. Due acknowledgement must always be made of the use of any material contained in, or derived from, this thesis.

Efren Guillo Sansano October 2018

#### Acknowledgements

I would like to express my sincere gratitude to my supervisors Dr. Andrew Roscoe and Prof. Graeme Burt for the continuous support, enthusiasm, immense knowledge and for the opportunity to conduct this research at Strathclyde.

Furthermore, I would also like to express my gratitude towards all my colleagues within the Advanced Electrical Systems and CDTs groups who have assisted me in numerous ways over the past few years. In particular, my research would have been impossible without the aid and support of Dr. Mazheruddin Syed and Richard Munro, with endless time spent in the dynamic power systems laboratory, recommissioning the lab and discussing on new technologies.

I extend my warmest thanks to my Spanish family in Glasgow for their invaluable support, encouragement and love.

Last but not least, I would like to thank my family: my parents Jose Luis and Pascualita, and my siblings Alvaro, Maria e Ivan, for always believing in me and supporting me during this long journey. Finally, a special thanks to Maria Jose for her understanding and love during all this time.

#### Abstract

Novel methods for the interface between the simulation and hardware of Power Hardware-In-the-Loop (PHIL) configurations have been analysed, developed and experimentally evaluated in this thesis, for enhancing the applicability of PHIL simulations, increasing its stability and accuracy performance.

Time delay is proven to be a critical limiting factor for PHIL simulations. Appropriately, a characterisation methodology for the time delay present within PHIL has been established, by which individual identification of time delay sources as well as time delay dynamics within the different components are reviewed. As a result, variable time delay has been identified within these configurations and mitigation techniques for the time delay and its variability are presented.

Furthermore, a time delay compensation scheme using Sliding Discrete Fourier Transform (SDFT) is demonstrated experimentally to improve the accuracy and stability of PHIL, even when harmonic components are present.

Detailed stability analysis of PHIL simulations performed provides clarification on the stability conditions of Ideal Transformer Method (ITM) Interface Algorithms (IAs). Additional improvements to PHIL IAs have been evaluated, with novel adaptive IAs established to provide enhanced stability.

Finally, enhancement of applicability of PHIL simulations is also experimentally proven with the implementation of an initialization process to a large scale power system application, in which the time delay compensation algorithm is also integrated.

# **Table of contents**

| Li | List of figures                 |                                      |    |  |  |  |  |

|----|---------------------------------|--------------------------------------|----|--|--|--|--|

| Li | ist of tables xvi               |                                      |    |  |  |  |  |

| G  | Glossary of Abbreviations xviii |                                      |    |  |  |  |  |

| 1  | Intr                            | oduction                             | 1  |  |  |  |  |

|    | 1.1                             | Research context                     | 3  |  |  |  |  |

|    | 1.2                             | Research contribution                | 7  |  |  |  |  |

|    | 1.3                             | Thesis structure                     | 8  |  |  |  |  |

|    | 1.4                             | List of publications                 | 9  |  |  |  |  |

| 2  | Pow                             | er Hardware in the Loop Challenges   | 12 |  |  |  |  |

|    | 2.1                             | Digital real-time simulation         | 13 |  |  |  |  |

|    | 2.2                             | Power amplifier                      | 14 |  |  |  |  |

|    | 2.3                             | Interface algorithms for PHIL        | 15 |  |  |  |  |

|    |                                 | 2.3.1 ITM                            | 16 |  |  |  |  |

|    |                                 | 2.3.2 Damping impedance method (DIM) | 18 |  |  |  |  |

|   | 2.4 | Time c   | delay within PHIL                                                                  | 21 |

|---|-----|----------|------------------------------------------------------------------------------------|----|

|   |     | 2.4.1    | Time delay compensation                                                            | 23 |

|   | 2.5 | Comm     | nunication interface                                                               | 24 |

|   | 2.6 | Initiali | zation of PHIL simulations                                                         | 24 |

| 3 | Tim | e delay  | characterization and mitigation of delay variability for PHIL                      | 1  |

|   |     | lations  |                                                                                    | 27 |

|   | 3.1 | Conve    | ntional time delay characterization                                                | 28 |

|   |     | 3.1.1    | Simulation platform delay, $T_{DRTS}$                                              | 29 |

|   |     | 3.1.2    | Communication delay, $T_{com}$                                                     | 30 |

|   |     | 3.1.3    | Power interface delay, $T_{PI}$                                                    | 32 |

|   |     | 3.1.4    | Delay introduced by other components and processes, $T_{other}$ .                  | 34 |

|   |     | 3.1.5    | Total delay, $T_d$                                                                 | 34 |

|   | 3.2 | Propos   | sed time delay characterization                                                    | 35 |

|   | 3.3 | Assess   | sment of delay variability impact on PHIL                                          | 38 |

|   |     | 3.3.1    | Impact of delay variability on stability                                           | 38 |

|   |     | 3.3.2    | Impact of delay variability on accuracy                                            | 39 |

|   | 3.4 | Experi   | mental validation of the proposed time delay characterization .                    | 42 |

|   |     | 3.4.1    | Case A: Validation with a time synchronized signal                                 | 43 |

|   |     | 3.4.2    | Case B: Validation with a PHIL platform with digital commu-<br>nication interface. | 46 |

|   |     | 3.4.3    | Case C: Validation with a PHIL platform with analog commu-<br>nication interface.  | 50 |

|   | 3.5  | Lessor   | as learned from the characterization of time delay         | 55 |

|---|------|----------|------------------------------------------------------------|----|

|   |      | 3.5.1    | Reducing time delay                                        | 55 |

|   |      | 3.5.2    | Mitigating and eliminating variability in time delay       | 57 |

|   | 3.6  | Conclu   | usions                                                     | 62 |

| 4 | Nov  | el time  | delay compensation algorithm for enhanced accuracy of PHIL | 1  |

|   | simu | ulations |                                                            | 64 |

|   | 4.1  | Time c   | lelay compensation                                         | 65 |

|   | 4.2  | SDFT-    | based time delay compensation algorithm                    | 67 |

|   |      | 4.2.1    | Sliding DFT algorithm                                      | 68 |

|   |      | 4.2.2    | Compensation and waveform reconstruction                   | 70 |

|   | 4.3  | Compe    | ensation algorithm considerations on stability of PHIL     | 71 |

|   | 4.4  | Accura   | acy performance of the time delay compensation algorithm   | 79 |

|   |      | 4.4.1    | Steady-state at nominal frequency                          | 80 |

|   |      | 4.4.2    | Voltage step                                               | 80 |

|   |      | 4.4.3    | Harmonic voltage step                                      | 82 |

|   |      | 4.4.4    | Frequency ramp                                             | 83 |

|   | 4.5  | Time c   | lelay compensation algorithm experimental validation       | 85 |

|   |      | 4.5.1    | Experiment configuration                                   | 85 |

|   |      | 4.5.2    | Performance characteristics                                | 88 |

|   |      | 4.5.3    | Steady-state experimental validation                       | 90 |

|   |      | 4.5.4    | Transient performance validation                           | 96 |

|   | 4.6  | Conclu   | usions                                                     | 99 |

|   |      |          |                                                            |    |

| 5 | Nov   | el interf | face algorithms for PHIL simulations                          | 101 |

|---|-------|-----------|---------------------------------------------------------------|-----|

|   | 5.1   | Adapti    | ve-ITM Interface Algorithm                                    | 102 |

|   |       | 5.1.1     | A-ITM Performance assessment                                  | 104 |

|   | 5.2   | Detaile   | ed stability conditions for PHIL                              | 109 |

|   |       | 5.2.1     | Routh-Hurwitz stability assessment                            | 109 |

|   | 5.3   | Virtual   | l impedance shifting method                                   | 114 |

|   |       | 5.3.1     | Implementation of virtual impedance shifting                  | 115 |

|   |       | 5.3.2     | Stability assessment                                          | 116 |

|   |       | 5.3.3     | Evaluation in a simulation environment                        | 121 |

|   | 5.4   | Conclu    | usions                                                        | 125 |

| 6 | A no  | vel PH    | IL initialization and synchronization approach for large powe | r   |

| U | syste |           | in intuitzation and synchronization approach for farge power  | 127 |

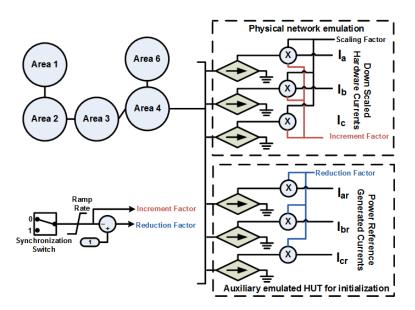

|   | 6.1   | PHIL i    | initialization and synchronization                            | 128 |

|   |       | 6.1.1     | Initialization issues                                         | 128 |

|   |       | 6.1.2     | Initialization of DRTS simulation                             | 129 |

|   |       | 6.1.3     | Synchronization                                               | 132 |

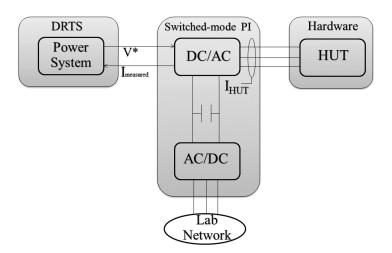

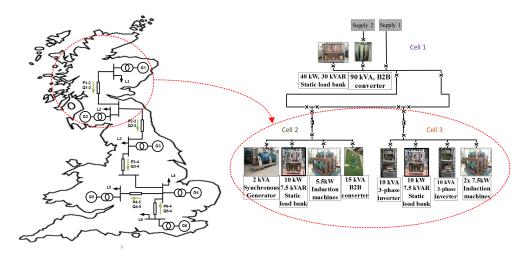

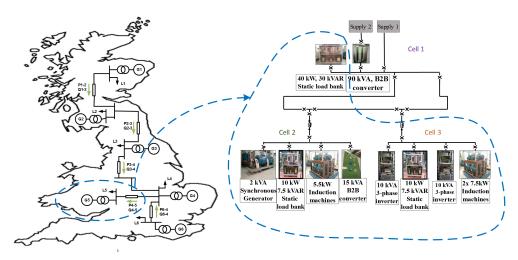

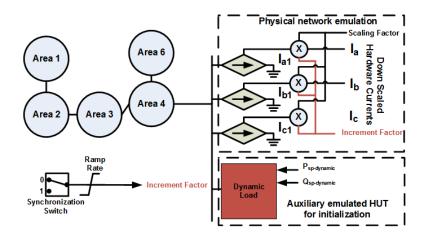

|   | 6.2   | PHIL (    | experimental configuration                                    | 135 |

|   |       | 6.2.1     | GB Power system                                               | 135 |

|   |       | 6.2.2     | Power interface                                               | 137 |

|   |       | 6.2.3     | HUT                                                           | 137 |

|   |       | 6.2.4     | Stability and accuracy considerations for the selected PHIL   |     |

|   |       |           | configuration                                                 | 139 |

|   | 6.3 | Experi   | mental assessment and validation                              | 140 |

|---|-----|----------|---------------------------------------------------------------|-----|

|   |     | 6.3.1    | Case Study A: HUT critical for the stability of the real-time |     |

|   |     |          | simulation.                                                   | 141 |

|   |     | 6.3.2    | Case Study B: HUT affecting voltage and frequency during      |     |

|   |     |          | initialization                                                | 145 |

|   | 6.4 | Conclu   | sions                                                         | 149 |

| _ |     |          |                                                               |     |

| 7 | Con | clusions | 5                                                             | 151 |

|   | 7.1 | Conclu   | sions                                                         | 151 |

|   | 7.2 | Further  | r Work                                                        | 154 |

|   |     | 7.2.1    | Adaptive interface algorithms                                 | 154 |

|   |     | 7.2.2    | Improve applicability of time delay compensation              | 155 |

|   |     | 7.2.3    | Online stability identification                               | 155 |

|   |     | 7.2.4    | Standardization of PHIL configurations and procedures         | 156 |

|   |     | 7.2.5    | PHIL with large penetration of power converters               | 156 |

|   |     |          |                                                               |     |

#### References

ix

157

# List of figures

| 1.1  | PHIL simple structure                                                      | 5  |

|------|----------------------------------------------------------------------------|----|

| 2.1  | Voltage and current type ITM IA                                            | 16 |

| 2.2  | PHIL control loop diagram                                                  | 17 |

| 2.3  | Diagram of DIM IA                                                          | 19 |

| 3.1  | PHIL time delay diagram with switched-mode amplifier                       | 29 |

| 3.2  | Time delay loop for DRTS and PI                                            | 36 |

| 3.3  | Nyquist plot of time delay effect on PHIL                                  | 40 |

| 3.4  | Simulation model for accuracy assessment                                   | 41 |

| 3.5  | Simulation assessment of stability and accuracy under variable time delay. | 42 |

| 3.6  | Experimental setup with time synchronized signal                           | 43 |

| 3.7  | Experimentally measured time delay variations                              | 46 |

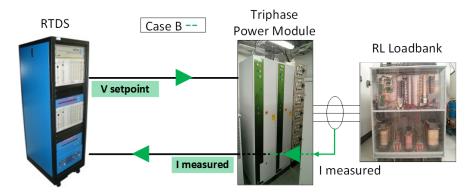

| 3.8  | Experimental setup for PHIL with digital link                              | 47 |

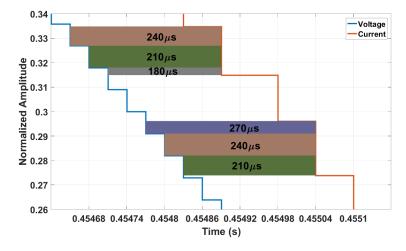

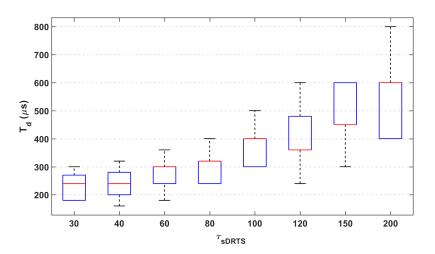

| 3.9  | Time delay assessment for every time step with $T_{DRTS} = 30 \mu s.$      | 48 |

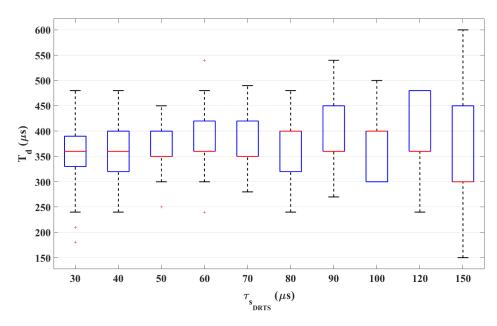

| 3.10 | Experimentally measured time delay for Case B                              | 49 |

| 3.11 | PHIL experimental setup with analog communication interface                | 51 |

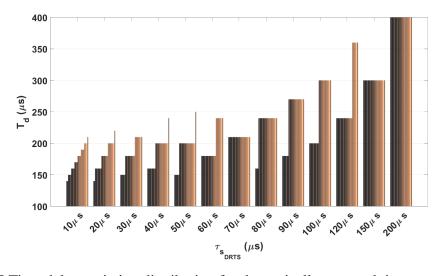

| 3.12 | Experimentally measured time delay for Case C                                                                                                                                                                                                                                                         | 54 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.13 | Time delay of PHIL with analog communication link                                                                                                                                                                                                                                                     | 54 |

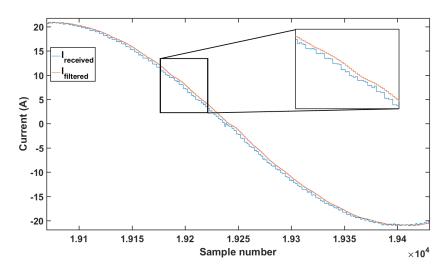

| 3.14 | Mitigation of delay impact with filter.                                                                                                                                                                                                                                                               | 58 |

| 3.15 | Time delay variation distribution for theoretically assessed time syn-<br>chronized signal.                                                                                                                                                                                                           | 62 |

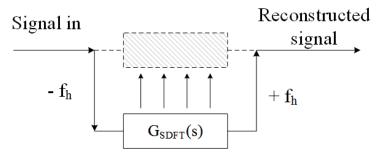

| 4.1  | PHIL with compensation algorithm                                                                                                                                                                                                                                                                      | 68 |

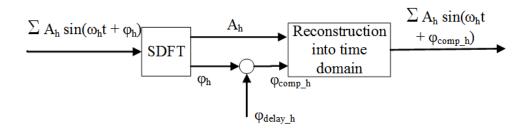

| 4.2  | Compensation algorithm diagram.                                                                                                                                                                                                                                                                       | 68 |

| 4.3  | SDFT algorithm diagram                                                                                                                                                                                                                                                                                | 69 |

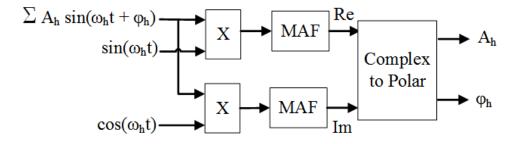

| 4.4  | Frequency response of SDFT and SDFT with reconstruction                                                                                                                                                                                                                                               | 72 |

| 4.5  | SDFT frequency shift diagram                                                                                                                                                                                                                                                                          | 72 |

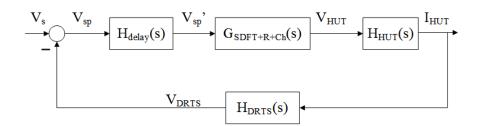

| 4.6  | Control loop diagram of PHIL with V-ITM and time delay compensation.                                                                                                                                                                                                                                  | 74 |

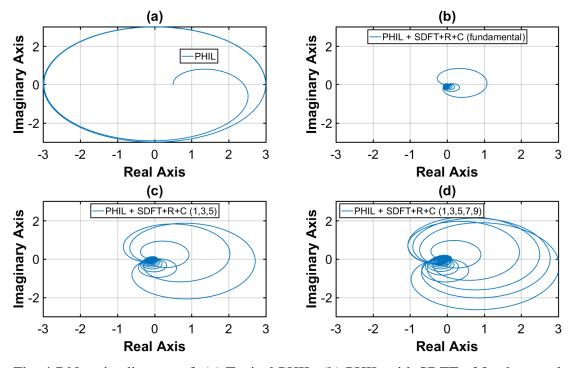

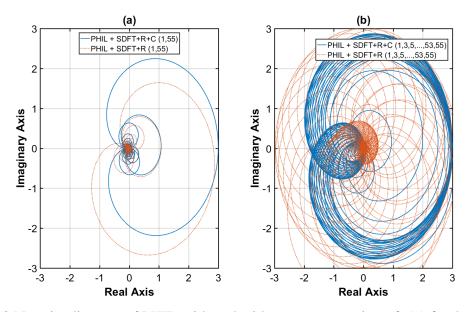

| 4.7  | Nyquist diagram of: (a) Typical PHIL, (b) PHIL with SDFT of funda-<br>mental frequency, (c) PHIL with parallel SDFT of fundamental and $3^{rd}$<br>and $5^{th}$ harmonics, (d) PHIL with parallel SDFT of fundamental, $3^{rd}$ ,<br>$5^{th}$ , $7^{th}$ , $9^{th}$ harmonics.                        | 75 |

| 4.8  | Nyquist diagram comparison with compensation added of: (a) Typical PHIL, (b) PHIL with SDFT of fundamental frequency, (c) PHIL with parallel SDFT of fundamental and $3^{rd}$ and $5^{th}$ harmonics, (d) PHIL with parallel SDFT of fundamental, $3^{rd}$ , $5^{th}$ , $7^{th}$ , $9^{th}$ harmonics | 76 |

| 4.9  | Nyquist diagram of PHIL with and without compensation of: (a) fundamental and $55^{th}$ , (b)odd harmonics up to the $55^{th}$ .                                                                                                                                                                      | 77 |

| 4.10 | Simulation model with compensation algorithm                                                                                                                                                                                                                                                          | 78 |

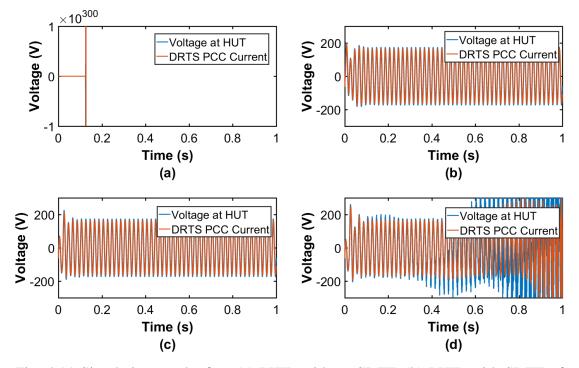

| 4.11 | Simulation results for: (a) PHIL without SDFT, (b) PHIL with SDFT                                                       |    |

|------|-------------------------------------------------------------------------------------------------------------------------|----|

|      | of fundamental frequency, (c) PHIL with SDFT of fundamental and $3^{rd}$                                                |    |

|      | and 5 <sup>th</sup> harmonics, (d) PHIL with SDFT of fundamental, 3 <sup>rd</sup> , 5 <sup>th</sup> , 7 <sup>th</sup> , |    |

|      | $9^{th}$ harmonics                                                                                                      | 78 |

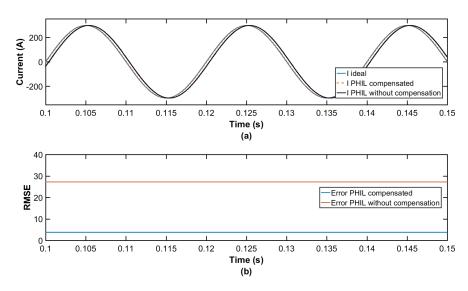

| 4.12 | Simulation results at steady state. (a) Steady-state current waveforms,                                                 |    |

|      | (b) error measurement                                                                                                   | 81 |

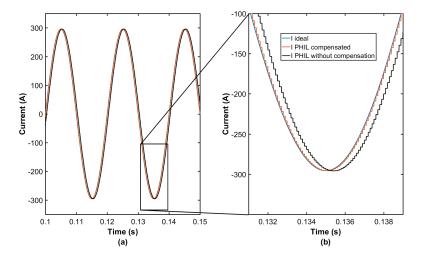

| 4.13 | Detail of the time delay at steady-state. (a) Currents, (b) zoomed currents.                                            | 81 |

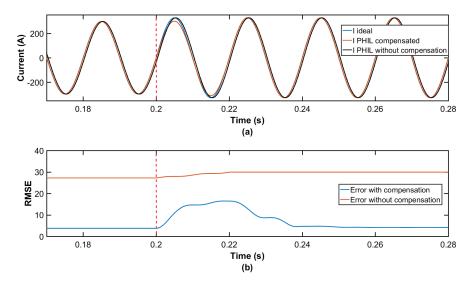

| 4.14 | Response of the PHIL implementation to a voltage step. (a) Current                                                      |    |

|      | responses, (b) error measurement.                                                                                       | 82 |

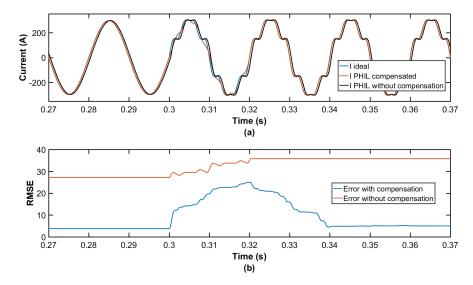

| 4.15 | Response of the PHIL implementation to harmonic component step. (a)                                                     |    |

|      | Current responses, (b) error measurement                                                                                | 83 |

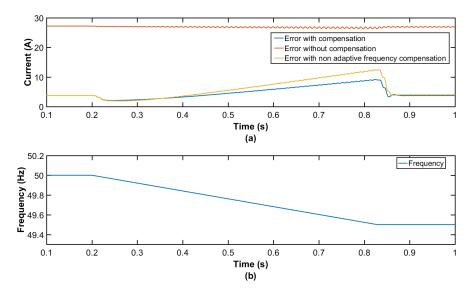

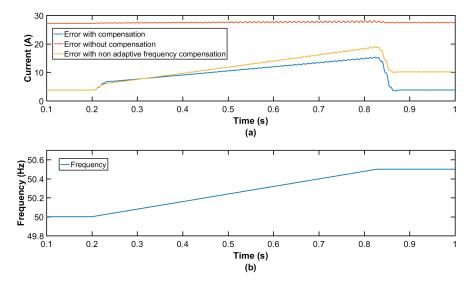

| 4.16 | Simulation results for a positive frequency deviation. (a) Error measure-                                               |    |

|      | ment, (b) frequency deviation.                                                                                          | 84 |

| 4.17 | Simulation results for a negative frequency deviation. (a) Error mea-                                                   |    |

|      | surement, (b) frequency deviation.                                                                                      | 85 |

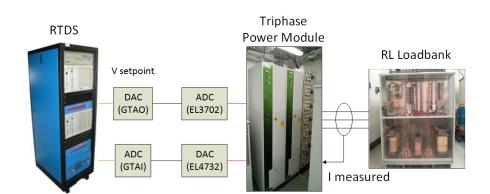

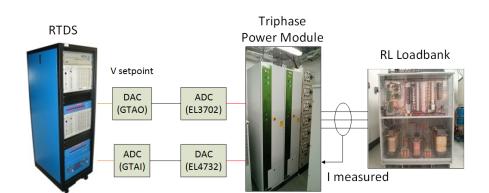

| 4.18 | PHIL experimental setup with analog communication interface                                                             | 86 |

| 4.19 | Switched-mode power amplifier configuration                                                                             | 88 |

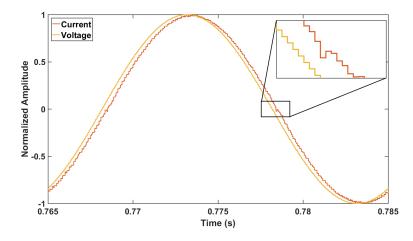

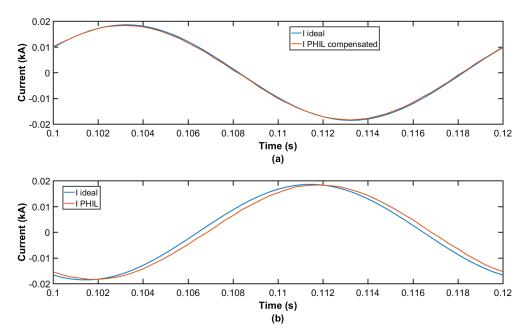

| 4.20 | Experimental measured currents at steady state                                                                          | 90 |

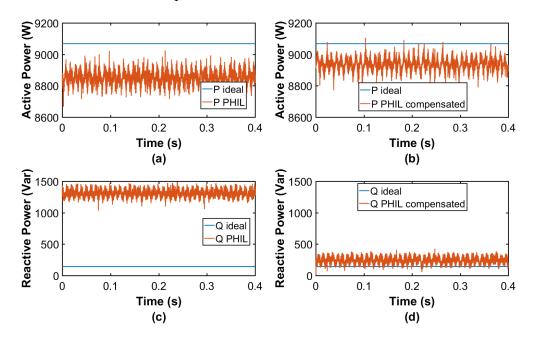

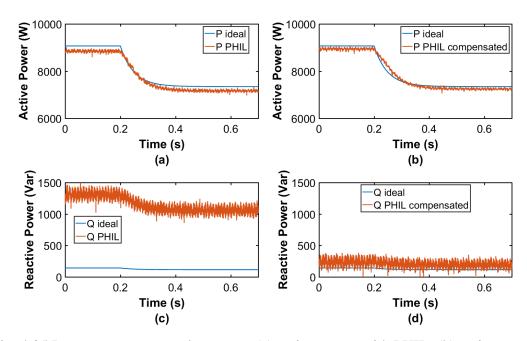

| 4.21 | Power measured at the simulation PCC for: (a) PHIL active power, (b)                                                    |    |

|      | PHIL reactive power, (c) compensated PHIL active power, (d) compen-                                                     |    |

|      | sated PHIL reactive power                                                                                               | 91 |

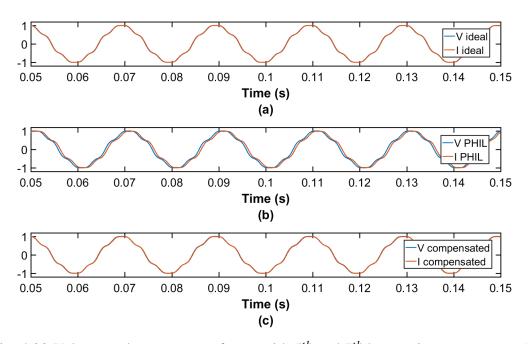

| 4.22 | Voltage and current waveforms with $5^{th}$ and $7^{th}$ harmonic components.                                           |    |

|      | (a) Ideal configuration, (b) conventional PHIL, (c) compensated PHIL.                                                   | 93 |

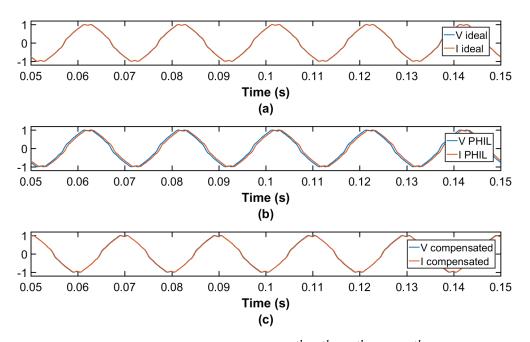

| 4.23 | Voltage and current waveforms with $5^{th}$ , $7^{th}$ , $11^{th}$ and $15^{th}$ harmonic components. (a) Ideal configuration, (b) conventional PHIL, (c) com-                       |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | pensated PHIL.                                                                                                                                                                       | 95  |

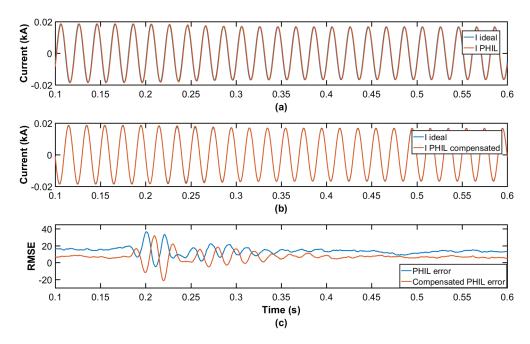

| 4.24 | Currents measured at the simulation PCC during a voltage step for (a)<br>PHIL implementation (b) compensated PHIL implementation. (c) Error<br>of both configurations.               | 97  |

| 4.25 | Power response to voltage step, (a) active power with PHIL, (b) active<br>power with compensated PHIL, (c) reactive power with PHIL and (d)<br>reactive power with compensated PHIL. | 98  |

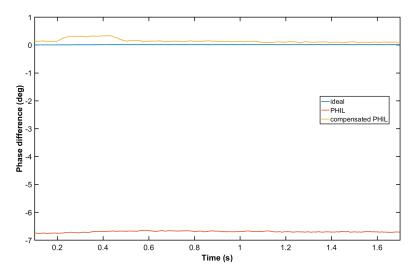

| 4.26 | Phase difference for a frequency ramp event                                                                                                                                          | 99  |

| 5.1  | Diagram of Adaptive-ITM IA                                                                                                                                                           | 103 |

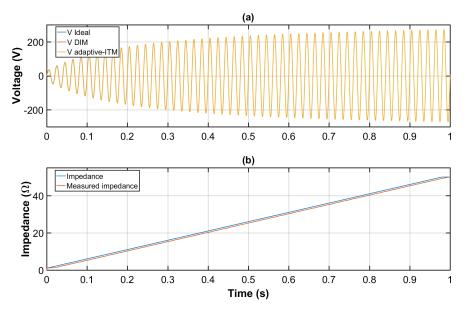

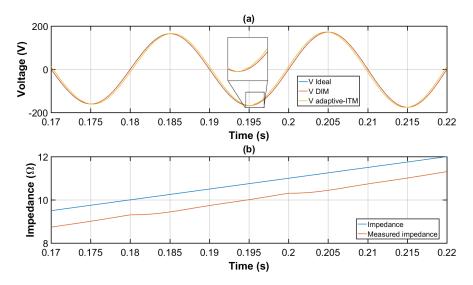

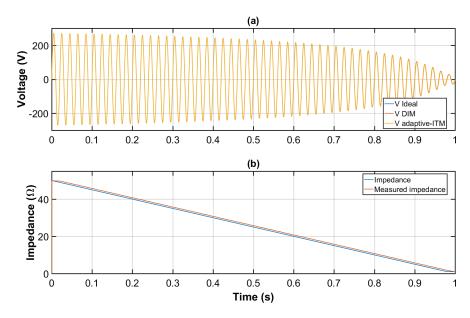

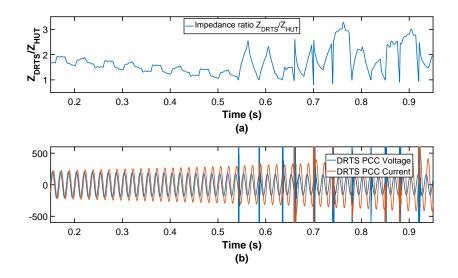

| 5.2  | Variable resistance simulation results and measured impedance values, from V-ITM to I-ITM                                                                                            | 105 |

| 5.3  | Zoomed simulation results and measured impedance values with vari-<br>able resistance, from V-ITM to I-ITM                                                                           | 105 |

| 5.4  | Variable resistance simulation results and measured impedance values, from I-ITM to V-ITM                                                                                            | 106 |

| 5.5  | Zoomed simulation results and measured impedance values with vari-<br>able resistance, from I-ITM to V-ITM                                                                           | 106 |

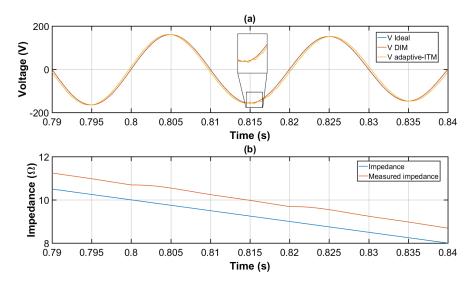

| 5.6  | Simualtion results for A-ITM with RL load.(a)Impedance ratio, (b)<br>Voltage and current measured.                                                                                   | 108 |

| 5.7  | PHIL control loop diagram.                                                                                                                                                           | 111 |

| 5.8  | Virtual impedance shifting diagram.                                                                                                                                                  | 115 |

| 5.9  | Control loop with virtual impedance shifting                                                                                                                                         | 116 |

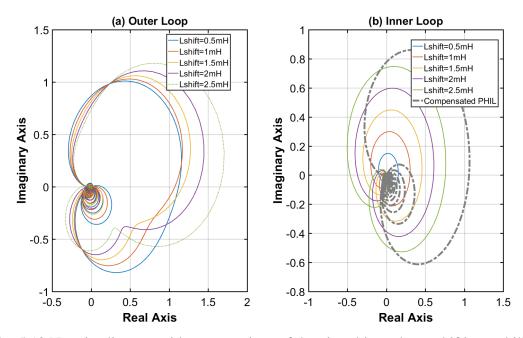

| 5.10 | Nyquist plot of virtual impedance shifting method for (a) open loop and       |      |

|------|-------------------------------------------------------------------------------|------|

|      | (b) closed loop transfer functions                                            | 119  |

| 5.11 | Control loop with virtual impedance shifting                                  | 120  |

| 5.12 | Nyquist diagram with a comparison of the virtual impedance shifting           |      |

|      | stability and SDFT                                                            | 122  |

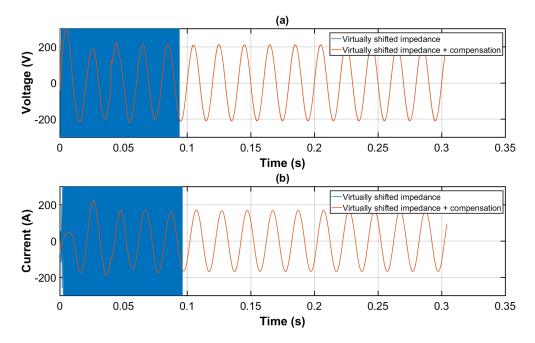

| 5.13 | Simulation results with $L_{shift} = 1.5mH$ for: (a) virtual impedance shift- |      |

|      | ing method and (b) virtual impedance shifting with time delay compen-         |      |

|      | sation                                                                        | 123  |

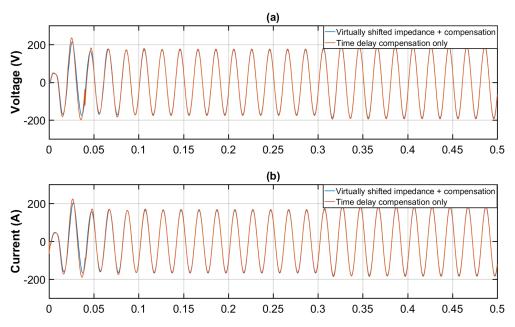

| 5.14 | Simulation results with $L_{shift} = 1.5mH$ for: (a) virtual impedance shift- |      |

|      | ing with time delay compensation and (b) only time delay compensation         | .124 |

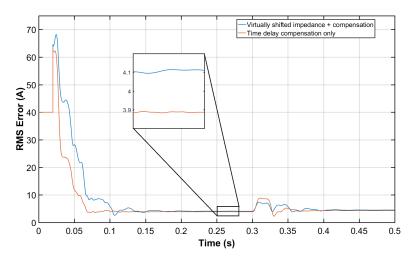

| 5.15 | RMS error of: (a) virtual impedance shifting with time delay compen-          |      |

|      | sation and (b) only time delay compensation.                                  | 124  |

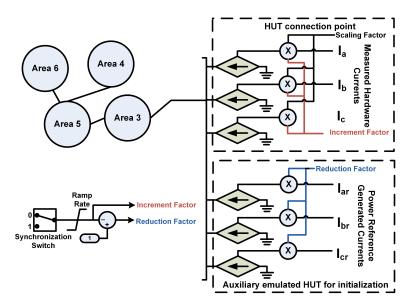

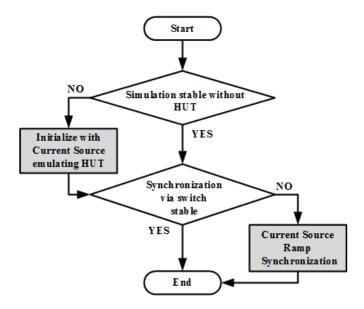

| 6.1  | PHIL initialization and synchronization structure used at DRTS                | 133  |

| 6.2  | Initialization and synchronization flowchart.                                 | 135  |

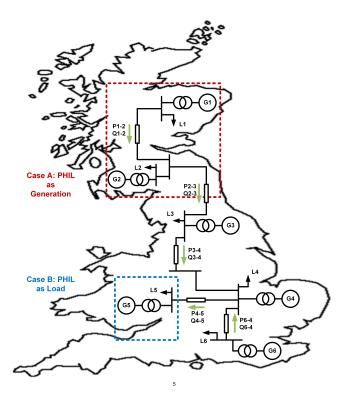

| 6.3  | Reduced six-bus dynamic model of the GB power system                          | 136  |

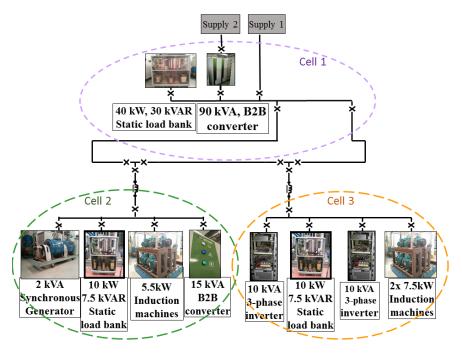

| 6.4  | Dynamic power system laboratory (HUT)                                         | 138  |

| 6.5  | System configuration for Case Study A                                         | 141  |

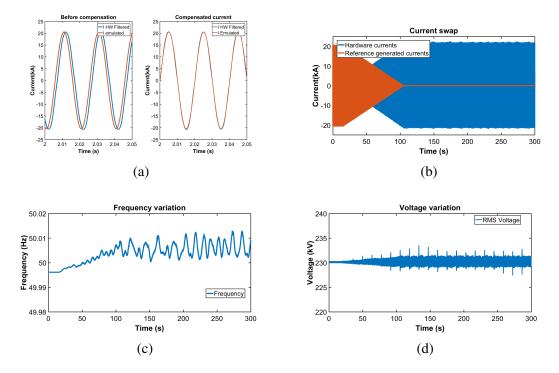

| 6.6  | Results for study case A: HUT critical for stability of RT simulation, (a)    |      |

|      | time delay compensation, (b) currents swapping during synchronization,        |      |

|      | (c) frequency at PCC during synchronization and (d) voltage at PCC            |      |

|      | during synchronization.                                                       | 144  |

| 6.7  | System configuration for Case Study B                                         | 145  |

| 6.8  | PHIL configuration for case study B with current source                       | 147  |

| 6.9  | PHIL configuration for case study B with dynamic load                         | 148  |

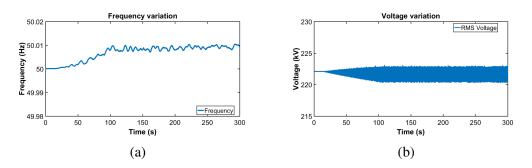

| 6.10 | Results for case B: affecting voltage and frequency during initialization |     |

|------|---------------------------------------------------------------------------|-----|

|      | (a) Frequency variation, (b) voltage variation                            | 149 |

## List of tables

| 3.1 | Theoretical time delay characterization                                                   | 45  |

|-----|-------------------------------------------------------------------------------------------|-----|

| 3.2 | Time delay of PHIL with digital communication link and $\tau_{sPI} = 66.667 \mu s$        | 50  |

| 3.3 | Time delay of PHIL with analog communication link and $\tau_{PI} = 1/16000$               | 53  |

| 3.4 | Constant delay calculation for range 1                                                    | 61  |

| 3.5 | Constant delay calculation for range 2                                                    | 61  |

| 11  | Common ant values for Nyquist discrem                                                     | 74  |

| 4.1 | Component values for Nyquist diagram                                                      | 74  |

| 4.2 | Phase error for experiment with presence of $5^{th}$ and $7^{th}$ harmonics               | 94  |

| 4.3 | Phase error for experiment with presence of $5^{th}$ , $7^{th}$ , $11^{th}$ and $15^{th}$ |     |

|     | harmonics                                                                                 | 96  |

| 5.1 | Component values for A-ITM with RL HUT simulation                                         | 107 |

| 5.2 | Routh-Hurwitz tabular method                                                              | 110 |

| 5.3 | Routh table with series RL HUT                                                            | 111 |

| 5.4 | Stability conditions for V-ITM                                                            | 113 |

| 5.5 | Stability conditions for V-ITM with added series $L_{sh}$                                 | 114 |

| 5.6 | Component values for stability assessment of virtual impedance shifting |     |  |

|-----|-------------------------------------------------------------------------|-----|--|

|     | method                                                                  | 118 |  |

| 6.1 | Area wise capacity and initial load condition.                          | 136 |  |

| 6.2 | Inter-area power flows.                                                 | 137 |  |

| 6.3 | Power setpoints for hardware components for case study A                | 143 |  |

| 6.4 | Power setpoints for hardware components for case study B                | 146 |  |

## **Glossary of Abbreviations**

| AC | <br>Alternating   | Current |

|----|-------------------|---------|

|    | <br>1 meetinating | Carrent |

- ADC ..... Analog to Digital Converter

- APF ..... Active Power Filter

- CHIL ..... Controller Hardware In the Loop

- DAC ..... Digital to Analog Converter

- DC ..... Direct Current

- **DER** ..... Distributed Energy Resource

- DFT ..... Discrete Fourier Transform

- DIM ..... Damping Impedance Method

- DPSL ..... Dynamic Power System Laboratory

- DRTS ..... Digital Real Time Simulation

- ESAC ..... Energy Source Analysis Consortium

- ETYS ..... Electricity Ten Year Statement

- FFT ..... Fast Fourier Transform

- GB ..... Great Britain

- GMPM ..... Gain Margin Phase Margin

- GPS ..... Global Positioning System

- GTAI ..... Giga-Transceiver Analog Input

- GTAO ..... Giga-Transceiver Analog Output

- HIL ..... Hardware In the Loop

- HUT ..... Hardware Under Test

- I-ITM ..... Current Ideal Transformer Method

- I/O ..... Input/Output

- IA ..... Interface Algorithm

- **IP** ..... Intellectual Property

- ITM ..... Ideal Transformer Method

- LHP ..... Left Half Plane

- MAF ..... Moving Average Filter

- NETS ..... National Electricity Transmission System

- PCC ..... Point of Common Coupling

- PCD ..... Partial Circuit Duplication

- PHIL ..... Power Hardware In the Loop

- PI ..... Power Interface

- PMU ..... Phasor Measurement Unit

- PV ..... PhotoVoltaic

- PWM ..... Pulse-Width Modulation

- **RES** ..... Renewable Energy Source

- RHP ..... Right Half Plane

- **RMS** ..... Root Mean Square

- **RMSE** ..... Root Mean Square Error

- ROS ..... Rest Of the System

- RTDS ..... Real Time Digital Simulator

- SDFT ..... Sliding Discrete Fourier Transform

- TSO ..... Transmission System Operator

- V-ITM ..... Voltage Ideal Transformer Method

- WAMPAC ..... Wide Area Monitoring Protection And Control

- ZOH ..... Zero Order Hold

### Chapter 1

## Introduction

Electric power systems can be operated in different manners, there exist AC (alternated current) operated systems, DC (direct current) and even hybrid systems where a mix of AC and DC is used. Such systems usually involve a variety of voltage levels and characteristics but they share a common aspect, all the devices within a power system are interconnected together by the use of transformers, converters, transmission lines, etc. Consequently, all of them influence the power system behaviour and operation, causing difficulties to understand complex power system interactions in its totality [KSE15].

The complexity of modern power systems is gradually increasing with the introduction of novel power components such as Distributed Energy Resources (DERs), Renewable Energy Sources (RES) or novel transformer or substation systems that are changing conventional power system dynamics [Dir17; The13; Bel15; Tat+13; KSE15]. The integration of such components requires the modification or development of current technology already installed such as instrumentation and control devices, challenging the reliability of the entire power system [Agu+17; ZSY14; DCW17; Mom+14; He+13]. This refers not only to land-based power systems, but also to marine, aeronautical or micro-grid electric systems with high penetration of power converters and complex devices that have an impact on power system dynamics [SVM16; Kim+15; He+13; SM15].

The design and development of power system components are usually performed through computer analysis and simulation [Mon+07a]. The integration of these components and their impact in the power system need to be assessed, this could be performed experimentally with real hardware but this implies a very high risk and cost that companies are not willing to take along with a lack of flexibility to perform a large variety of test scenarios; therefore, offline simulation is commonly used for this purpose [Kot+15]. However, simulation studies introduce a number of concerns:

- A complete simulation of the power system is very difficult to achieve due to its complexity and the limitations of the software tools and computers.

- Usually there is a number of different proprietary software for the existing devices in the network that rarely will be available on its entirety [BT10; KSE15].

- Interaction between developed device simulation models and power system may not be accurately included on detailed device models developed by manufacturers [KSE15].

These obstacles are increasing the concern on testing methodologies for power system components as previous techniques (only simulation or pure hardware) are no longer affordable (in terms of time and cost) or accurate enough. As a consequence, significant effort has been performed during the last few years in the development of computer capabilities for the simulation of detailed electrical power systems in real-time [FS15], enabling the study and application of different testing procedures that are able to address the increased need for accurate testing of electrical components, improving the accuracy, cost and risk of traditional test procedures [Bla+16; Pal+17; VDC17]

The first step towards the development of new testing procedures for power components was demonstrated with the development of Hardware-in-the-Loop (HIL) simulation technique, which is able to merge the two traditional testing procedures (pure simulation and hardware) by interfacing the software simulation with the real hardware under test.

For the purpose of facilitating the assessment of the integration of complex devices or devices with unavailable proprietary software (e.g. for controllers), HIL simulation technique presents promising characteristics. This approach allows for external hardware components to be coupled with a simulated system running in real-time. Real-time simulation is needed for HIL test-beds as hardware components are coupled to the simulation, which require of a real-time exchange of information [Pal+17].

Depending on the testing scenario, a power system simulation model will have to be developed in a real-time simulation platform. These platforms can present limitations in terms of computational power, consequently the size and fidelity of the models can be limited. However, typically the power system model will try to capture the main dynamics of the system and the interactions with other components in order to provide a representative model for the hardware under test (HUT) to be accurately tested [BT10]. The behaviour of the real device within its proposed environment can be explored under relative safety conditions with minimal risk of damage to the actual hardware. The proposed environment and test scenarios can be expanded from normal conditions to include extreme events which may be difficult or dangerous to recreate in reality, but which represent events during which the device should maintain stable operation.

#### **1.1 Research context**

HIL simulations enable the implementation of very detailed and exact hardware components in a laboratory environment for its testing and development. Commonly HIL simulations are separated into two different categories, Controller-HIL (CHIL) and Power-HIL (PHIL), depending on the type of interface required for coupling the simulated system with the Hardware Under Test (HUT) [Ngu+18]. The interface is selected in accordance with the type of HUT to be tested. More precisely, these testing methodologies are defined as:

1. CHIL

The exchange of information between the simulated Rest Of the System (ROS) and the hardware component is only composed by control signals and accordingly the hardware being coupled is usually "secondary" power system components such as instrumentation or controllers that only require of a low voltage and low power signal to be transmitted between them, hence the reason why sometimes this is also known as secondary HIL. However, since just low level signals are exchanged between the software simulation and the HUT, this procedure is not valid for power components such as motors, generators or power converters that require higher levels of power to be exchanged.

2. PHIL

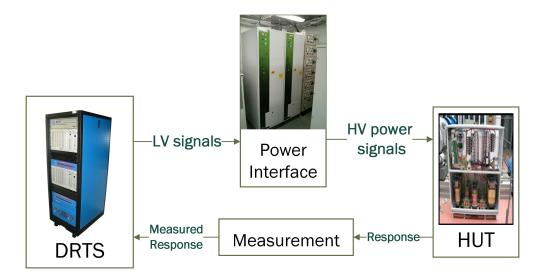

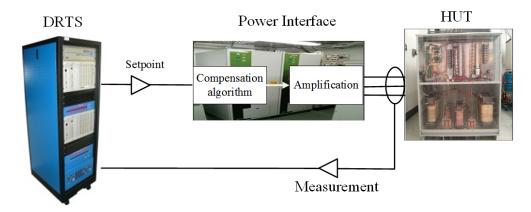

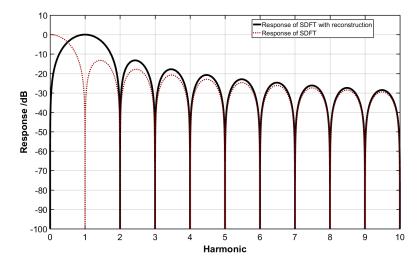

When the HUT requires the exchange of higher level power signals to operate, a Power Interface (PI) is required to sit between the simulated ROS and the HUT. The PI converts the low voltage/power signals of the Digital Real-Time Simulator (DRTS) into high voltage/power signals as well as provides electrical coupling between both subsystems. The HUT responds to the PI amplified signal (current or voltage), and the measurement of this response is fed back (by the power interface or an external measurement unit) to the DRTS, closing the loop as shown in Fig. 1.1.

For developers of devices, CHIL allows them to prove and de-risk the performance and design of instrumentation and control systems in a safe and inexpensive test bed. When primary hardware prototypes are added in a PHIL environment, their entire

Fig. 1.1 PHIL simple structure

design (not only instrumentation and control) can also be de-risked [Edr+15]. However, detailed power system models of the network to which developed devices may be connected (the simulated part) may not be available. Indeed, often there is no single specific network, or if there is a specific network, its details may be proprietary or not fully understood accurately. The important aspect is for the designers to subject the device to a wide range of simulated scenarios which cover the full and worst-case range of conditions that the hardware might encounter during its lifetime [RGB16; KKK17].

HIL techniques allow power system network owners to create reasonably accurate models of their networks in simulation, since they will have access to the network design data. Then, they can place manufacturer-supplied controllers or primary hardware connected to their simulated systems. The network owner will rarely have access to the proprietary software contained inside the manufacturer device, so it is generally not possible to model the combined system entirely in simulation [BT10]. However, the manufacturer device can be supplied as a boxed unit and the Intellectual Property (IP) protected. The network owner can then run tests and assess the performance of the device within its specific network environment, thereby de-risking the deployment of the real product on their network [RGB16].

However, the implementation of PHIL also presents a number of challenges mainly due to the fact that the system is composed of two subsystems (the simulation and the HUT) which are now interconnected by means of a power interface, which is not part of the original system [Mon+07b]. The addition of the PI in pursuance to achieving higher power levels does imply some challenges, as the interface is not part of the original system and therefore it can modify the dynamic behaviour of the system under test, affecting the accuracy and stability of the simulation [Lau+16].

The main challenges associated with PHIL simulations which are investigated in this thesis are:

- Time delay: The communication required between the simulation, the power interface and the measurement of the HUT response, introduces a loop delay that can affect to the accuracy and stability of PHIL simulations [Gui+14; GRB15; Jon11; RSW07]. Therefore, the loop delay needs to be clearly understood, identified and mitigated when possible for the achievement of safe and accurate PHIL testing.

- 2. Stability: The interface algorithms, which are responsible of the electrical coupling between the simulation and the HUT, together with the partition of the power system in two subsystems, are decisive elements for the stability of PHIL simulations [RSB08]. The stability of PHIL simulations must be ensured before the testing starts, as real equipment is being tested.

- 3. Accuracy: The accuracy of PHIL depends mainly on: the accuracy of the PI, the precision of the communication channel, the sensors used for the measurements and the interface algorithm used [Leh+12]. Furthermore, the total time delay of the PHIL configuration will play a major role in the accuracy of the results [GRB15]. In order to validate novel power system components and their interaction the results must be accurate.

4. Initialisation of PHIL simulation: The simulation and hardware need to be initialised and achieve steady-state in a controlled manner, before the testing of dynamic scenarios is initiated. This condition is unlike a simulation-only environment where various techniques can be used to pre-configure states and integrators so that the simulation begins at steady-state. In the HIL environment, the device designer will be forced to anticipate through the startup, initialisation, and other sequences that are imperative to get the device working from a "cold start" [Gui+18].

#### **1.2 Research contribution**

The main contributions from this thesis are summarized as:

- Realization and implementation of a novel method to accurately characterize the time delay of PHIL implementations, which provides a far more comprehensive and detailed analysis than previous approaches. Accordingly, stability and accuracy of PHIL implementations can now be accurately assessed, reducing the risk and uncertainties.

- Identification of variability in time delay within PHIL simulations, along with an analysis of the impact of the variability in PHIL stability and accuracy. Furthermore, the dynamics of the time delay variability has been integrated within the characterization method.

- Development of a method for mitigating variable delays with the introduction of an optimization algorithm for the simulation time step, aiming at the reduction of the noise of the signals on the implementation and consequently on improving the accuracy of PHIL.

- Design, analysis and validation of a new method for the compensation of time delay in PHIL implementations, which is based on phase-shifting of the phasors in a phase-by-phase and harmonic-by-harmonic manner. Hereby, PHIL simulations are now capable of accurately reproducing the existing power exchanges between simulation and hardware during steady-state conditions.

- PHIL stability analysis for ensuring a correct interpretation of the stability conditions is always achieved, avoiding misleading stability assessments.

- Development and analysis of a novel adaptive interface algorithm to cope with interface algorithms limitations, more precisely to improve the stability performance of PHIL simulations.

- Development and evaluation of a novel virtual shifting impedance method based on the stability requirements of PHIL simulations. By virtually shifting the impedance, this method accomplishes to avoid the physical shifting of components to achieve stability, increasing the applicability of the method.

- Simultaneous implementation of virtual shifting impedance method alongside the time delay compensation method, which leads to an enhanced stability performance.

- Establishment of an initialization approach for PHIL simulations to solve the limitations that the testing of power components or systems, which are not able to initialize without the other subsystem being initially connected, were bringing to PHIL simulations.

#### **1.3** Thesis structure

The structure adopted for the completion of this thesis is presented below.

Chapter 2 introduces the main challenges existent within PHIL simulations that the contributions within this thesis aims to solve. Chapter 3 demonstrates the presence of a variable time delay in PHIL simulations and also proposes a time delay characterization approach for such implementations. Chapter 4 proposes a novel time delay compensation algorithm for the improvement of accuracy and stability of PHIL simulations. Chapter 5 presents two novel interface algorithm developments along with a detailed stability assessment of their implementation within a PHIL simulation. Chapter 6 illustrates an initialization approach for the implementation of PHIL simulations in a larger variety of applications. Finally, chapter 7 collects the conclusions and summarises the contributions from this thesis, further work identified from the results of this thesis is also presented.

#### **1.4** List of publications

The publications which have resulted from the work completed in this thesis are:

**E. Guillo-Sansano**, M. H. Syed, A. J. Roscoe, G. M. Burt, F. Coffele, "Time Delay Characterization for the Improvement of Power Hardware-in-the-Loop Simulations," *IEEE Transactions on Industrial Electronics* (under review).

Y. Wang, Y. Xu, Y. Tang, K. Liao, M. H. Syed, **E. Guillo-Sansano**, G. Burt, (in press) "Aggregated Energy Storage for Power System Frequency Control: A Finite-Time Consensus Approach," *in IEEE Transactions on Smart Grid*.

**E. Guillo-Sansano**, M. H. Syed, A. J. Roscoe, G. M. Burt, "Initialization and Synchronization of Power Hardware-In-The-Loop Simulations: A Great Britain Network Case Study." *Energies 2018*, 11, 1087.

V. H. Nguyen, Y. Besanger, Q. T. Tran, T. L. Nguyen, C. Boudinet, R. Brandl, F. Marten, A. Markou, P. Kotsampopoulos, A. A. van der Meer, **E. Guillo-Sansano**, G. Lauss, T. I.

Strasser, K. Heussen, "Real-Time Simulation and Hardware-in-the-Loop Approaches for Integrating Renewable Energy Sources into Smart Grids: Challenges & Actions", *in IEEE PES Innovative Smart Grid Technologies ISGT Asia 2017*.

C. Steinbrink, S. Lehnhoff, S. Rohjans, T.I. Strasser, E. Widl, C. Moyo, G. Lauss,

F. Lehfuss, M. Faschang, P. Palensky, A.A. van der Meer, K. Heussen, O. Gehrke,

E. Guillo-Sansano, M. H. Syed, A. Emhemed, R. Brandl, V.H. Nguyen, A. Khavari,

Q.T. Tran, P. Kotsampopoulos, N. Hatziargyriou, N. Akroud, E. Rikos, M. Z. Degefa

(2017) "Simulation-Based Validation of Smart Grids – Status Quo and Future Research

Trends." *In: Mařík V., Wahlster W., Strasser T., Kadera P. (eds) Industrial Applications of Holonic and Multi-Agent Systems*. HoloMAS 2017. Lecture Notes in Computer

Science, vol 10444. Springer, Cham.

M. H. Syed, **E. Guillo-Sansano**, S. M. Blair, G. M. Burt, H. Brunner, O. Gehrke, J. E. Rodriguez-Seco "Laboratory infrastructure driven key performance indicator development using the smart grid architecture model," *in CIRED - Open Access Proceedings Journal*, vol. 2017, no. 1, pp. 1866-1870, 10 2017.

E. O. Kontis, G. K. Papagiannis, M. H. Syed, **E. Guillo-Sansano**, G. M. Burt, T. A. Papadopoulos, A. I. Chrysochos, "Development of measurement-based load models for the dynamic simulation of distribution grids," *2017 IEEE PES Innovative Smart Grid Technologies Conference Europe (ISGT-Europe)*, Torino, 2017, pp. 1-6.

Roscoe, A., **Guillo-Sansano, E.** and Burt, G. (2016). Physical Hardware-in-the-Loop Modeling and Simulation. *In Smart Grid Handbook (eds C. Liu, S. McArthur and S. Lee)*.

**E. Guillo-Sansano**, M. H. Syed, A. J. Roscoe, G. Burt, M. Stanovich and K. Schoder, "Controller HIL testing of real-time distributed frequency control for future power systems," 2016 IEEE PES Innovative Smart Grid Technologies Conference Europe (ISGT-Europe), Ljubljana, 2016, pp. 1-6. M. Chen, M. H. Syed, E. Guillo-Sansano, S. D. J. McArthur, G. M. Burt and I. Kockar, "Distributed negotiation in future power networks: Rapid prototyping using multi-agent system," 2016 IEEE PES Innovative Smart Grid Technologies Conference Europe (ISGT-Europe), Ljubljana, 2016, pp. 1-6.

**E. Guillo-Sansano**, M. H. Syed, P. Dambrauskas, M. Chen, G. M. Burt, S.D.J. McArthur, T. Strasser, "Transitioning from centralized to distributed control: Using SGAM to support a collaborative development of web of cells architecture for real time control," *CIRED Workshop 2016*, Helsinki, 2016, pp. 1-4.

**E. Guillo-Sansano**, A. J. Roscoe and G. M. Burt, "Harmonic-by-harmonic time delay compensation method for PHIL simulation of low impedance power systems," 2015 *International Symposium on Smart Electric Distribution Systems and Technologies* (*EDST*), Vienna, 2015, pp. 560-565.

**E. Guillo-Sansano**, A. J. Roscoe, C. E. Jones and G. M. Burt, "A new control method for the power interface in power hardware-in-the-loop simulation to compensate for the time delay," *2014 49th International Universities Power Engineering Conference (UPEC)*, Cluj-Napoca, 2014, pp. 1-5.

### Chapter 2

# Power Hardware in the Loop Challenges

The main challenges that arise from a PHIL implementation are due to the fact that the test system is divided into two subsystems: i) a simulated system in real-time and ii) the HUT, both required to be interconnected by means of a power interface. The interface is a non-ideal component that is added to the test system modifying its characteristics. The main challenges for PHIL are therefore introduced by the interface, which challenges the stability and accuracy of the simulations [Ngu+18; Jon11; RSW07]. The effects that the complete interface is bringing into the test system need to be clearly analysed and understood in order to find a solution that approximates the behaviour and results of the PHIL simulation as much as possible to an ideal pure hardware testing scenario, achieving accurate and stable PHIL simulations for any test scenario.

Thus, the elements that compose the interface for PHIL simulations are required to be identified, these are:

- 1. Physical components: DRTS, power amplifier and the communication interface.

- 2. Interconnection attributes: interface algorithm and time delay.

Accordingly, the main features of the elements that form the interface of PHIL simulations are introduced in this section for an initial analysis of the challenges associated to each element.

Additionally, initialization challenges of PHIL simulations are also introduced in this chapter, as it can also bring limitations into the applicability of the PHIL simulations. This is mainly due to the stability of each subsystem, which may be dependent on its interconnection with the other subsystem, leading into a challenging initialization procedure.

#### 2.1 Digital real-time simulation

In [Far+15], DRTS of electric power systems is defined as "the reproduction of output (voltage/currents) waveforms, with the desired accuracy, that are representative of the behaviour of the real power system being modeled". Furthermore, detailed description of the hardware and software that comprises a DRTS (such as processors, solvers, modelling tools, communication interfaces) are also reported in [Far+15].

The main feature of DRTSs utilized for PHIL simulations is their use of fixed time-step solvers for providing real-time operation. However, this necessary condition also brings limitations in terms of the simulated models size and level of detail that can be used. This is due to the requirement of performing all the calculations for the simulated model within the assigned time-step and for every time-step during the complete simulation duration, otherwise unstable or unreliable performance can be achieved [Lan+13; Lau+16].

Accordingly, the time-step of the DRTS needs to be selected in accordance with the complexity of the simulated model and the maximum bandwidth required for the model to be accurate (of importance when simulation of power electronic components is required).

#### 2.2 Power amplifier

Three different power amplifier types are typically used for PHIL simulations: linear, switched-mode and synchronous generator type amplifiers. A comparison between them and a discussion on their impact on PHIL simulation has been presented in [Leh+12]. When the power amplifiers are used for interfacing purposes, such as when used for PHIL applications, it can be also identified as the power interface (PI).

- Linear amplifiers are composed of transistors operating in the linear region, which present a very high dynamic performance with a short time delay [Leh+12; VLF11; Kot+15]. However, their cost and large losses typically limit their use for high power levels. These power amplifiers have been used for the testing and validation of power components and systems with PHIL simulation in [Leh+12; VLF11; Kot+15; NW15; Mar+17].

- In the other hand, switched-mode amplifiers are typically preferred for high power applications as their efficiency and flexibility is greater, although a larger time delay and slower dynamics exist typically in this case [Leh+12; Ste+10]. In [KGW17; JMJ15; Ben+11; Dar+14; SLS13], the design, development, control, and commissioning of switched-mode amplifiers of different power levels (kVA up to MVA) have been presented. Also, in [Dav18; MKB18] an analysis of the dynamics of this amplifier type is presented along with stability studies.

- The use of synchronous generator type amplifiers for PHIL applications is limited due to the slow response of the generators and a lack of flexibility for applications with unbalances and fast dynamics [Leh+12; Ros+10; Ros+11b].

Both linear and switched-mode amplifiers are typically characterised as a time delay and a second order transfer function (commonly that of a low pass filter) [Ren07]. This function reduces the gain of the higher frequency components, assisting to improve the stability performance of PHIL simulations [Bra17]. However, actual power amplifier technology can reproduce a high number of harmonic components, therefore having a considerable high cut off frequency for the low-pass filter behaviour, allowing an accurate simulation for test systems where high frequency components are not involved. The dead-time of switched-mode amplifiers has been demonstrated to also have a slight impact into the stability as presented in [MKB18]. The time delay associated with the power amplifier is typically combined with other time delays of the PHIL configuration and is analysed in a separate section of this chapter.

#### 2.3 Interface algorithms for PHIL

An interface can be defined as a shared boundary with information exchanges between the involved sections. For PHIL implementations the boundary is at the electrical Point of Common Coupling (PCC) of the HUT with the DRTS and the information exchanged are the voltages and currents. The specification of this interface for PHIL is defined as the Interface Algorithm (IA). This specification includes the type, quantity, and function of the interconnection circuits and the type and form of signals to be interchanged by these circuits [Edi00].

An analysis of different IAs proposed in the literature for PHIL simulations have been presented in [RSB08; Bra17]. From these analysis, the Ideal Transformer Method (ITM) and Damping Impedance Method (DIM) IAs are suggested as the most reliable ones for performing PHIL simulations in terms of stability and accuracy. This is in agreement with the large majority of PHIL simulations, which typically implement these IAs [Kot+12; Man+17; Lan+12; HTP17; LS18; Hok+18]

Therefore, only an introduction of these IA methods is presented here. Furthermore, a conventional stability assessment performance of the selected IAs is also presented.

#### 2.3.1 ITM

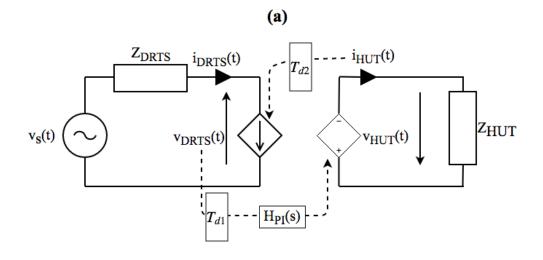

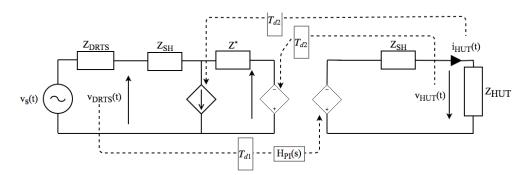

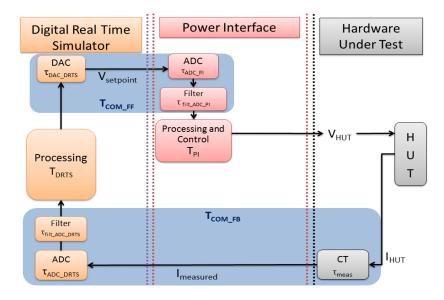

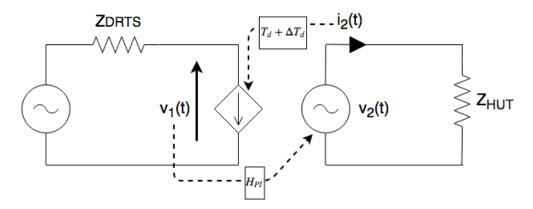

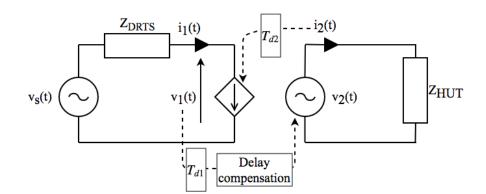

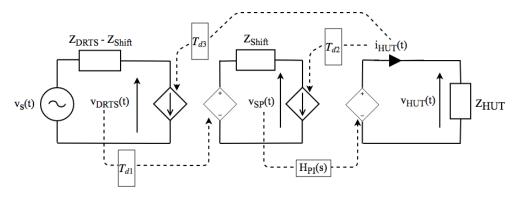

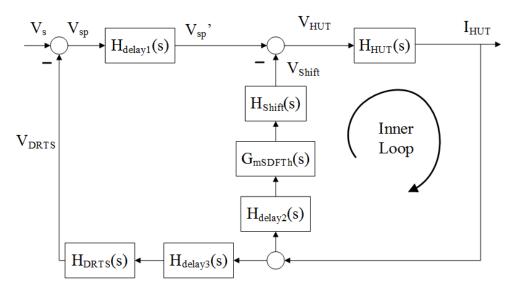

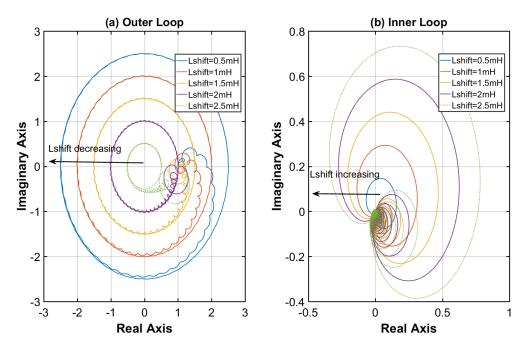

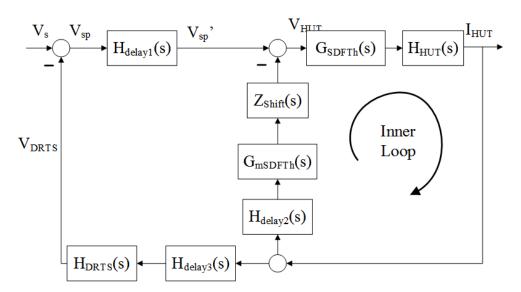

This IA method was originally described in [Kuf+95], and later applied to PHIL in [RSB08], where two different types of interface were described depending on the signal being amplified, voltage-type ITM (V-ITM) when the voltage is the amplified signal and current-type ITM (I-ITM) when the current is amplified. Schematics of these two IAs are presented in Fig. 2.1, where  $Z_{DRTS}$  and  $Z_{HUT}$  represent the total impedance of the simulation and HUT respectively.  $T_{d1}$  and  $T_{d2}$  symbolize the time delay of the feed-forward and feedback path.  $H_{PI}$  is the power interface transfer function.

(b)

Fig. 2.1 Voltage and current type ITM IA

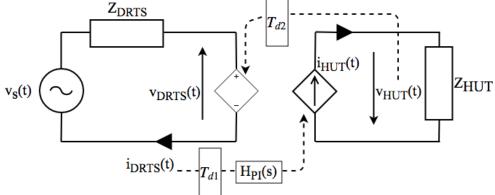

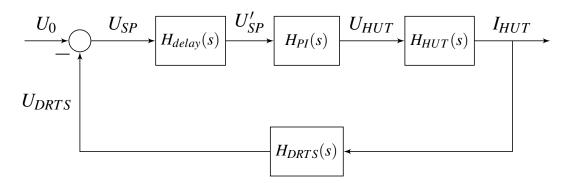

Fig. 2.2 PHIL control loop diagram.

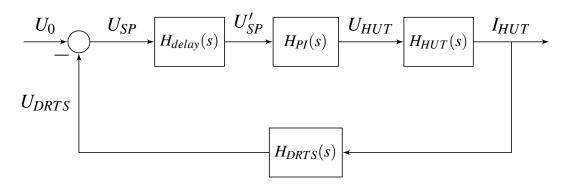

The stability of PHIL simulations using ITM IA has been broadly discussed in the literature. Conventional stability assessments as presented in [RSB08; DGL14; Lau+11; Jon11; LLS12; HRM16; Edr+15; Bla+17; KKK17] conclude that the stability of ITM IA depends on the ratio of impedances, with some of them referring only to resistive impedances ratio [Lau+11; Jon11; KKK17] and others to impedance magnitude ratio [RSB08; DGL14; Edr+15; LLS12]. Therefore, according to these studies, to achieve a stable simulation under V-ITM (when the PI is assumed ideal, unity gain and zero time delay) the ratio of impedances must be  $|Z_{HUT}(s)| > |Z_{DRTS}(s)|$ . On the contrary, when I-ITM is implemented the condition is the opposite  $|Z_{HUT}(s)| < |Z_{DRTS}(s)|$ . These conditions are commonly established from an stability assessment of the open loop transfer function derived from the control diagram of Fig. 2.2 (for V-ITM in this case) where:

$$H_{HUT}(s) = \frac{I_{HUT}(s)}{U_{HUT}(s)} = \frac{1}{Z_{HUT}(s)}$$

(2.1)

$$H_{DRTS}(s) = \frac{U_{DRTS}(s)}{I_{HUT}(s)} = Z_{DRTS}(s)$$

(2.2)

$$H_{delay}(s) = e^{-sT_d} \tag{2.3}$$

where  $H_{delay}$  is the transfer function of the total delay of the PHIL simulation, and  $T_d = T_{d1} + T_{d2}$  the total accumulated time delay.  $H_{HUT}$  is the HUT transfer function and  $H_{DRTS}$  the DRTS transfer function.

The open loop transfer function  $H_{OL}(s)$ , of the control loop presented in Fig. 2.2 can be represented as:

$$H_{OL}(s) = \frac{U_{DRTS}}{U_0} = H_{delay}(s) \cdot H_{PI}(s) \cdot H_{HUT}(s) \cdot H_{DRTS}(s)$$

(2.4)

With the power interface considered ideal,  $H_{PI}(s)$  is equal to 1. This is typically considered as it does not negatively affect to the stability assessment [MKB18] due to its filtering behaviour, hence  $H_{OL}(s)$  can be simplified as:

$$H_{OL\_V-ITM}(s) = e^{-sT_d} \frac{Z_{DRTS}(s)}{Z_{HUT}(s)}$$

(2.5)

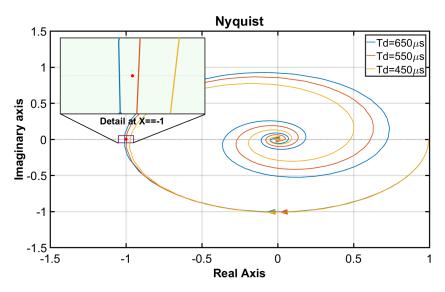

For fulfilling the Nyquist stability criterion, with  $e^{-sT_d}$  characterizing a phase reduction as the frequency increases, literature suggests the ratio  $|Z_{DRTS}(s)|/|Z_{HUT}(s)|$ must be less than 1 in cases where  $X_{DRTS} = 0$  and  $X_{HUT} = 0$  for not encircling the point (-1, 0) and achieve a stable simulation. Similar assessment of the stability can be performed for I-ITM, producing:

$$H_{OL\_I-ITM}(s) = e^{-sT_d} \frac{Z_{HUT}(s)}{Z_{DRTS}(s)}$$

(2.6)

yielding the opposite condition to V-ITM, by which the ratio  $|Z_{HUT}(s)|/|Z_{DRTS}(s)|$ must be less than 1.

#### **2.3.2** Damping impedance method (DIM)

This IA has been presented in [RSB08] as a combination of ITM and Partial Circuit Duplication (PCD) IAs. A diagram with the topology of DIM IA is presented in 2.3, where  $Z^*$  represents the damping impedance, which for achieving an accurate simulation should be equal to  $Z_{HUT}$ . The open loop transfer function of this configuration has been presented in [RSB08; Bra17; KKK17] as:

Fig. 2.3 Diagram of DIM IA

$$H_{OL\_DIM}(s) = \frac{Z_{DRTS}(s)(Z_{HUT}(s) - Z^*(s))}{(Z_{HUT}(s) + Z_{SH}(s)(Z_{DRTS}(s) + Z_{SH}(s + Z^*(s)))}e^{-sT_d}$$

(2.7)

This IA would always be stable if  $Z^* = Z_{HUT}$  as the numerator would be equal to zero; however, considerable knowledge of the HUT would be required for achieving such condition. With one of the purposes of PHIL simulations being the testing of proprietary equipment and black-box devices, this appears as an impractical interface. Nevertheless, online impedance identification of the HUT is complex but feasible as demonstrated in [Ric+17; PE13; Ric+16; RMM18; LRM16; SS14], although practically large window periods are required, for example 100*ms* is used in [Ric+17], which can risk the accuracy and stability of the simulation as the impedance will need to be modified in real-time as the HUT varies. When harmonic components and non-linear loads are present, accurate impedance identification becomes very challenging [Ric+17]. Furthermore, DIM IAs typically requires of a linking impedance which can affect to the dynamics of the system under test.

This method can therefore be limited by high penetration of converter connected generation, along with the increase of non-linear apparatus that will bring an increase in the effect of harmonic components as well as faster dynamics into future power systems. As a result, most of the PHIL simulations for research and validation of power components and systems are being performed with the ITM method due to its straightforward implementation as well as its good accuracy, although its stability performance is not optimal [Bla+17; Kot+15; GRB15].

Accordingly, the developments proposed in this thesis have been mainly implemented with ITM IA, although some of the developments are independent of the IA and could be applied for any of the presented IAs.

From the presented ITM algorithm characteristics, it can be concluded that it is important to improve the stability of ITM IAs without affecting the good accuracy performance that it provides. Consequently, a number of interface compensation methods for the improvement of ITM IAs have been presented in the literature:

- Filtering of the feedback current: a straightforward implementation presented in [Lau+11; Kot+12] in which the addition of a low pass filter in the current feedback path of the PHIL implementation provides an improvement of the stability by limiting the frequency bandwidth of the system. However, considerable time delay is introduced by the filter which reduces the accuracy of the ITM IA implementation.

- Addition of hardware inductance: in [Kot+15; Hon+09] the stability of inductor coupled systems is studied, resulting in an increased stability of the system when part of the simulation inductance is shifted from the simulation into the hardware for V-ITM IAs.

- Multi-rating interface: in this case the digitally simulated model is partitioned into subsystems with smaller time steps which can improve the stability as presented in [LLS12; LS18]. Still, this method requires of the limitation of the bandwidth through feedback filters which affects to the accuracy.

#### 2.4 Time delay within PHIL

The total loop delay of PHIL simulations affects the stability of the simulation, but it is often overlooked due to the importance of the IA, mainly the relationship between impedances at both sides of the interface for achieving a stable simulation when using ITM or the accuracy of the impedance estimation when DIM is used [RSB08; Tre+17].

It has been concluded from different studies that the time delay has a big impact on the accuracy of the simulation and that it has to be reduced and compensated for an accurate implementation [HTP17; HRM16; YG12; GRB15; Li+18]. This is even more relevant when evaluation of harmonic components is to be performed, as the lag of harmonic phases will be larger than at the fundamental component.

The effects that the time delay introduces into the accuracy and stability of PHIL simulation can be summarize as:

• Time delay effect on accuracy of PHIL

The main accuracy aspect affected by the time delay is the phase difference introduced between the voltage and current at the simulation PCC, that consequently affects the apparent power factor of the HUT and hence the active and reactive power exchanges are inaccurate when compared with an ideal scenario [GRB15; Li+18; Ros+10]. If interaction of the harmonic components of the HUT are acknowledged as part of the PHIL simulation, their phase relationship will be even more altered by the time delay leading to low accuracy results [Gui+14; GRB15]. Voltage and current waveforms have to be measured at the PCC in the DRTS system for detecting the time delay introduced and the accuracy effect in the phase relationship between voltage and current. Accordingly, the time delay introduced in PHIL applications needs to be measured, reduced and compensated in order to have more accurate simulations. • Time delay effect on stability of PHIL

Stability is a crucial element to consider before implementing a PHIL simulation since an unstable PHIL configuration could cause fatal damage to the HUT and PI, and hence stability studies are usually performed before the implementation of PHIL simulations [Jon11; Lau+16]. The IA plays an important role for studying the stability of PHIL simulations as each specific IA presents particular characteristics (different signals to be exchanged, electrical elements) and therefore depending on the IA selected the time delay can have different effects on the stability.

Most of the contributions on PHIL in the literature acknowledge that time delay is important [Kot+15; LLS12; Ren+11; Lau+11; Kot+12; Gui+14; Li+18; Zha+16], however a detailed study of time delay has not been performed yet. Such a study would help better understanding of the time delay and the PHIL configuration for reducing the latency to the minimum for an improved PHIL simulation. Appropriate understanding of the time delay and its effects will lead to a reduced risk for performing PHIL experiments and at the same time it can help to increase its accuracy by mitigating and reducing the delays. Hence, identification of the components and processes that introduce the delay seems as the first step towards a better understanding. However, previous work on PHIL simulations only focus on the total or average loop delay without detailing why is the time delay produced or how it can be reduced for improving dynamic and transient behaviours of PHIL simulations [Gui+14; RSW07; Li+18; Zha+16].

For the purpose of achieving a more accurate and stable implementation of PHIL simulations, a detailed study of the time delay introduced by the different PHIL components is required. This will allow for a recommended PHIL implementation practice for achieving reduced time delays. At the same time, it will facilitate the development of compensation techniques for the time delay, which are required for stable and accurate PHIL implementations.

#### 2.4.1 Time delay compensation

In addition, for an accurate PHIL simulation, the identified time delay needs to be compensated. Different time delay compensation techniques have been presented in the literature, these are:

- Lead compensator: Lead compensation can be used for the idealization of nonideal interface gain [Ren+11; PH17], nonetheless this method can significantly amplify high frequency components and its applicability for complex systems and when harmonic components are present is limited.

- Fast Fourier Transform (FFT) compensation: this method consists on phaseshifting the different frequency signals according to the time delay after an FFT has pre-processed the signals [RSW07], although the use of a fixed base frequency can impair the accuracy if the frequency changes. It compensates up to the 13<sup>th</sup> harmonic due to the large computational time required to process FFTs.

- Fundamental dq compensation: time delay of the fundamental component is compensated in this case by adding an additional phase term into the dq to abc coordinate transformation [Li+18; Zha+16]. Nevertheless, when unbalanced or very distorted signals are present its accuracy can be limited, besides in this case only fundamental components have been compensated.

- Synchronous generator control compensation: in [Ros+10] a phase advance introduced into the control of the synchronous generator provides the compensation of the fundamental frequency component.

However, the presented techniques may not be sufficiently accurate when more complex networks with non-linear components (producing harmonic components) are being tested. Therefore, the need of an optimized compensation technique which takes into account the dynamics of complex power systems is identified.

#### 2.5 Communication interface

Traditionally, analog communication interfaces have been utilized for establishing the transmission of data between DRTS and power amplifier, and also between the measured response of the HUT and DRTS [GRB15; HTP17; Kot+15]. The use of analog communication links requires of digital to analog conversion at the DRTS due to the digital nature of the DRTS, besides when switched-mode power amplifiers are used an additional analog to digital conversion is required, as the implemented control of the power amplifier is typically performed with a digital controller. Similarly, for the return path of the HUT measurement, further analog to digital conversion is required for integrating the measurement within the digital simulator.

The operation of an analog communication link is accompanied by the introduction of noise and uncertainties through the digital to analog converters (DACs) and analog to digital converters (ADCs), which can present offset errors, gain errors and noise proceeding from quantization errors [Fer+15].

On the other hand, high-speed digital communication interfaces can also be utilized for PHIL simulations [KGW17; Jen17], optimizing the interface when digital devices (as the DRTS and the controller of the switched-mode power amplifier) are part of the configuration. This configuration is generally more accurate due to the absence of ADC and DACs, mitigating the noise and uncertainties typically introduced by those components. Also, minimal time delay will be introduced into PHIL simulations with the implementation of a digital communication interface [KGW17].

#### 2.6 Initialization of PHIL simulations

Frequently, PHIL simulations are carried out for the testing of single devices or where the HUT represents a relatively small part of the network in comparison with the simulated rest of the system at the DRTS [Lan+12; Nae+15; Kot+13; PH17]. Nevertheless, this balance in PHIL between hardware and software is insufficient for other scenarios such as the validation of wide area monitoring, protection and control (WAMPAC) systems (an area of increasing interest given recent advancements in phasor measurement units (PMU) [ZCN11]) or distributed HIL simulations [Ste+17b; Lun+17; Cal+18]. In these cases, the different subsystems will be of variable size and importance, not just a simple power component but a portion of a power system, which may be required for the stable operation of the complete system. The HUT subsystem connected to the simulation subsystem can represent generation or load components, consisting of many devices interconnected or just a simple significant device. The conventional approach for setting up a particular PHIL simulation involves the following steps:

- The power network within the DRTS is initialized, achieving steady-state.

- Interface signals from the initialized DRTS simulation are then amplified by the power interface.

- The HUT response to the reproduced signal is measured and fed back to the DRTS for closing the loop, coupling both subsystems electrically.

For power systems studies, the load and generation conditions along with the power transfer at points of interest are selected from known scenarios [Gui+18]. This allows for testing under known stress conditions of the network or particular scenarios of interest. For example, a previously measured pre-fault condition of the network may be considered, where a novel control algorithm can be tested in order to evaluate if its implementation could have improved the response to the event. Accordingly, when PHIL simulations are initialized and the loop is closed, it is important to ensure that the conditions at all the buses of the test network (including the HUT terminals) are equivalent to the initial expected ones.

When the HUT is relatively small compared to the DRTS simulated power system [Lan+12; Nae+15; Kot+13], the DRTS simulation can be initialized without the HUT, hence the power system within the DRTS performs as a grid whose voltage and frequency are not dependent upon the HUT to be connected. Under these circumstances, the HUT is typically synchronized with the DRTS simulation by means of a simple switch, electrically coupling the HUT with the DRTS. Operation of the switch can introduce transient behaviours; however, when a stiff simulated grid or a modest HUT is present, the transient does not pose a significant risk for achieving a stable operating point at the start of the study. The initialization process as well as the electrical synchronization between the two subsystems (the closing of the loop) are thus relatively straightforward.

On the other hand, for cases where the network is not a stiff grid and the HUT is significant for the grid (either to be capable to initialize without it, or to remain stable if it is directly connected) an initialization procedure for the simulated part of the system including a reliable synchronization procedure is required.

# **Chapter 3**

# Time delay characterization and mitigation of delay variability for PHIL simulations

The time delay present in PHIL implementations is one of the important factors affecting stability and accuracy, therefore it is essential to identify and analyse time delay sources and their impact in a PHIL implementation. Accordingly, the first step towards the assessment of the time delay is to identify the components and processes that introduce time delay throughout the PHIL simulation loop. Then, an analysis of the interaction between the delays introduced by the different components is required. When the time delay sources and interactions have been identified, accurate characterization of the time delay is possible.

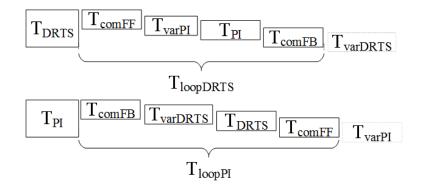

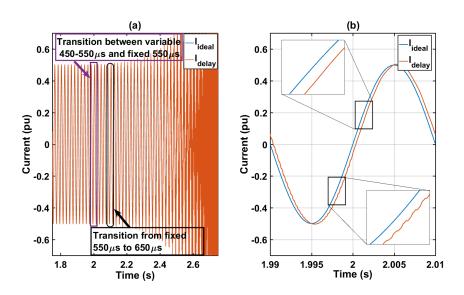

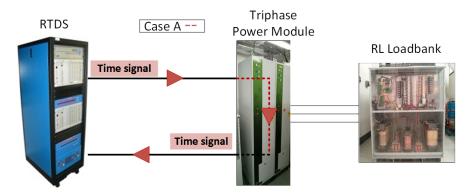

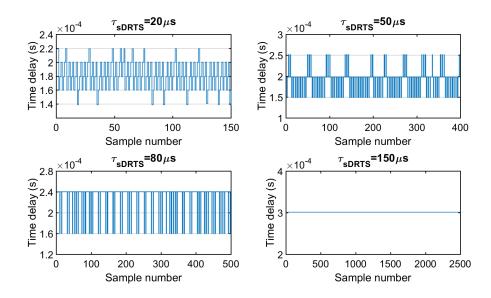

With the time delay source identification and the analysis of the interactions between the delays, variability in time delay due to the interaction of different fixed time steps from the components typically involved in the PHIL process has been identified, and its significance on stability and accuracy is studied in this chapter. Appropriate understanding of the time delay and its effect leads to reduced risk of instabilities and inaccuracies when performing PHIL experiments and at the same time it can help to increase its accuracy by mitigating and reducing the delays.

Therefore, with the aim of providing a detailed characterization of time delays for PHIL simulations, this chapter contributions are as follows:

- A detailed analysis of time delays associated with PHIL simulations is undertaken to characterize the identified delays. Generic equations that characterize the time delay have been developed, allowing for an accurate analytical assessment of the time delay in PHIL setups.

- Contrary to the common assumption of a constant time delay, it is shown that time delay associated with a PHIL setup is typically variable.

- The impact of the identified variability in time delay on the stability and accuracy of PHIL setups is presented.

- Measures to mitigate the impact of the variability in time delay and ultimately eliminate it are proposed.

- The validity of the time delay characterization, the presence of variability in time delay and the measures proposed to mitigate or eliminate the variability are experimentally verified.